コンピュータの電力効率を高めるために何をすべきか?

1946年に完成したENIACでは1万7000本の真空管を使ったが、それらをつなぐため人手で500万カ所のはんだ付けを行ったという。集積回路の貢献は、1万7000本の真空管に相当するトランジスタを集積したこともあるが、500万カ所のはんだ付けを集積したことが重要であるという。

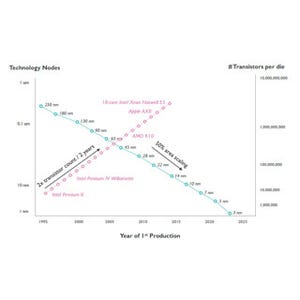

トランジスタ単体の消費電力が減らず、性能が上がらなくなるポストムーアの時代には、電力の低減を行わないと性能を上げることはできなくなる。そして、そのために重要な技術が、接続の改善であると黒田先生は言う。

現在の接続の主流は、機械式(配線、はんだ付け、コネクタ)接続であるが、これを電子式(近接場結合)に革新することで接続のバンド幅や消費電力を改善することができるという。

電磁波(光を含む)は近接場と遠方場があり、遠方場は電波として遠くまで届くが、近接場は距離が離れると急速に減衰し、ごく近所にしか届かない。しかし、接続という用途では、遠くには届かず、混信しない近接場の方が向いている。

磁界を使うThruChip Interface(TCI)

TCIは、具体的には微小なコイルを上下のダイに作り、対向させて磁界で信号を伝送する。磁界はシリコンチップを貫通できるので、上下のダイの間で信号を送受することができる。

コイルでは磁界の変化分しか受信できないが、次の図の中央に示したラッチ型のセンスアンプを使えば、右側の波形のように、元の信号と同じ綺麗な方形波の信号を受け取ることができる。

この回路は標準のCMOSプロセスで作ることができ、TSVのような特殊な追加プロセスを必要としない。また、コイルはSRAM素子の上などに作っても良く、チップ面積的にも負担が小さい。

次の図はTCIでの通信距離とデータ伝送バンド幅の関係を示すものであり、240μm角のコイルを使うと80μmまで伝送でき、10μm厚のダイ9枚の間の通信ができる。しかし、伝送速度は22Gbpsに抑えられる。一方、コイルを小さくして、60μm角のコイルを使うと20μm程度の距離の伝送しかできないが、80Gbpsという高速で信号を伝送できる。

また、TCIでは、次の図のようにコイルの角の部分をオーバラップして配置して、4相の多重化を行うことにより、コイル面積を縮小することができる。

次の表に示すように、TSVを作るためには追加のプロセスが必要であり、チップのコストが標準CMOSと比べて40%程度高くなってしまう。一方、TCIは標準のCMOSプロセスで作れ、チップコストの上昇は数%程度に抑えられる。そして配置の自由度が高く、信号伝送速度も高い。加えて、消費電力も低いと良いことずくめである。

7nmプロセスのCMOSトランジスタと組み合わせた場合、シミュレーションでは、50μm厚のチップの場合は150μm角のコイルを使い2Tbit/s/mm2の伝送速度が得られる。したがって、1mm×8mmのチップ面積で18Tbit/sの信号を伝送でき、消費電力は0.5Wである。

また、チップの厚みを25μmと半減すると、コイルは75μm角と小さくでき、伝送速度は11Tbit/s/mm2に向上する。そして1mm×8mmの面積で91Tbit/sのデータを2.2Wで伝送できる。

TCIの場合、電源接続はどうするのか?

TSVはスタックしたダイを貫通して金属配線で接続するので、信号だけでなく、電源、グランドを接続することができる。しかし、TCIでは直流は伝送できないので、電源の供給を行うことはできないという欠点がある。

これに対して、黒田先生は「HDSV(Highly Doped Silicon Via)」という手法を提案する。HDSVでは、CMOSトランジスタを作るP-wellやN-wellの形成よりも高い濃度で不純物のイオン打ち込みを行い、低抵抗のシリコンによるビアを形成する。通常の10倍程度の濃度であれば、 CMOS製造に使っている普通のマシンでイオン打ち込みを行うことができ、コストアップもわずかであるという。

右下の2つのグラフはNとPの不純物を1×1016/cm2と1×1017/cm2で打ち込んだ場合のシリコンビアの抵抗値を示すもので、1016の場合はダイの厚みが5μm以下であれば3mΩ以下、1017の場合は10μm以下の厚みなら3mΩ以下の抵抗が得られる。なお、ビアの大きさは7mm×0.1mmである。

このシリコンビアの表裏にアルミの電極を付け、表面を平坦できれいにして接触させると、分子間力で接着してしまう。なお、この図では常温と書いてあるが、SC15で微小なタングステンビアを使うシステムをデモしていたTezzaronは、接着を確実にするため200℃程度に加熱していると言っていた。

3mΩでは大電力のCPUチップに給電するのは難しいが電力の低いメモリチップには使えそうである。

次の図の左端はNAND Flashチップをずらして積層し、ワイヤボンドで信号や電源を接続する現在の実装を示している。左から2番目の図はダイを5μmピッチまで薄くし、TCIとHDSVを使った場合で、16ダイを積層しても厚みは80μmでI/Oエネルギー/ビットは1/400以下となるという。

右側はDRAMの積層の場合で、TSVを使うとダイピッチは55μm程度である。右端はTCI+HDSVでDRAMを積層した場合で、ダイピッチ8μmでI/Oエネルギー/ビットはTSVの場合と比べて1/10以下になるという。