シミュレーションの結果

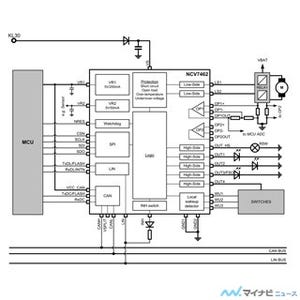

オン・セミコンダクターのI3T50テクノロジ(350nmスマート・パワー・テクノロジ)を採用し、表3に記載した主要特性を持つ、つまり極端な動作条件と素子のプロセスばらつき(「低速」はMOSトランジスタの低トランスコンダクタンス、低ゲート静電容量、高スレッショルド電圧を意味し、「高速」はその逆)を包含した設計済み回路を使用して、提示LDOの動作を検証しました。

各シミュレーションでは、標準プロセス・パラメータと動作条件(VIN=8V、VDD=3.3V、Iload=50mA、Cext=50nF、外部コンデンサのESRとESLはどちらも0、温度27℃)の公称値動作を使用しました。プロットで、公称値動作の結果は黒の太い実線、低温時動作の結果は寒色(青)の細い実線、高温時動作は暖色(赤、オレンジ、黄色)の細い破線で表記しました。

LDOのレギュレーション(VFB)ループの開ループ電圧ゲイン(図13に示す)は、分数次数挙動を示しています。45°位相という広い領域があるからです。低周波数時は、左側を終端したRCラダーを使用していること、および外側の極がほとんど影響を及ぼさないため位相が大きくなります。高周波数時は、位相が大きくなる(ESRとESLのため)か、小さくなります(寄生極のため)。UGFのアダプティブ調整が原因で、UGFは大きく変化します。

図14にプロットしたDC負荷特性は、LDOで非常に厳密なDCレギュレーション(小さい動的出力抵抗)が実現されていることを示します。これは、誤差アンプを(分数次数)積分器として使用する利点です。アダプティブUGF調整が原因で、この特性は凸型(出力電流が小さいときに動的出力抵抗が大きい)になっています。

素子のミスマッチをシミュレーションに含めた場合(ミスマッチ・モンテカルロ分析または感度分析による)、負荷電流が0から最大値(50mA)の範囲全体で、出力電圧は4.936V~5.073Vの範囲(6シグマ区間)で変化します。

負荷電流が0mAから50mAに増加したときのLDOのステップ応答を図15にプロットします。負荷電流が50mAから0mAに減少したときのLDOのステップ応答を図16にプロットします(三角形の部分は、出力電圧のオーバシュートによって外部コンデンサが急速充電され、その後、負荷電流によって徐々に放電されることを表現しており、LDOは自身の出力から大きな電流をシンクできない)。応答のセトリング部分(三角形部分を除く)は、ほぼ単調な変化であり、レギュレーション・ループに十分な位相マージンが存在することを示唆しており、形状はMittag-Leffler関数に調和しています(つまり、最初の急速な減衰は、指数関数で想定される場合より長い期間、引き延ばされている)。

(次回は11月9日の掲載予定です)

著者プロフィール

Pavel Horský (パヴェル・ホルスキー)オン・セミコンダクターの技術スタッフのメンバーで、専門分野はEMC、ESD、信頼性を重視した自動車用アナログ/ミクスド・シグナルIC設計。

1997年から、アルカテル・マイクロエレクトロニクス、AMIセミコンダクター、オン・セミコンダクターで、アナログおよびミクスドシグナル・デザインエンジニア、テクニカル・プロジェクト・リーダー、アナログASIC設計グループのリーダーを歴任。

チェコ共和国ブルノ工科大学で、1994年にラジオエレクトロニクス理学士号、1998年に計測学で博士号を取得。

2011年から同大学准教授として、博士課程の学生向けにアナログデザインコースを担当。60の出版物の著者および共同著者、15の米国特許の起草および共同起草者。

Libor Kadlčík (リボル・カドルーク)

オン・セミコンダクターのチェコ共和国にあるデザインセンターで、アナログASIC設計グループに所属。

チェコ共和国のブルノ工科大学で、2011年に電子通信学の理学士号、また2013年に理学修士号を取得。

現在、同大学の電子通信技術(D-EST)プログラムの博士号を取得中。