LDOの説明

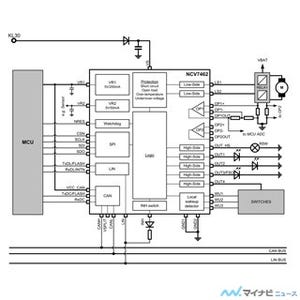

分数次数誤差アンプはLDO(図10に回路図を示す)で採用されています。このLDOに内蔵されているコントローラの出力は電流IDRV(s)を駆動し、最終段ミラーでこの電流を増幅して出力電流IOUT(s)を生成します。

コントローラ自体で、アクション電圧VACT(s)で制御される駆動段が駆動電流IDRV(s)を生成し、誤差アンプがこの電流を出力します。誤差アンプは、電圧分割器を使用してLDOの出力電圧を監視します。誤差アンプと他の低電圧ブロックは、低電圧電源VDD(電圧はVDD)から電力が供給されます。この電源は、他のオンチップ電圧レギュレータから電力が供給されます。

LDOのレギュレーション・ループに関する小信号ACモデルを図11に示します。LDOの各ブロックで観察される信号の周波数特性を図12に示します。誤差アンプのトランスインピーダンスZe(s)は、セクション2で取り上げた、両端を終端したRCラダーのインピーダンスに近い値です。

レギュレーション・ループの開ループ電圧ゲインは、次のとおりです。

図11と図12で図示するレギュレーション・ループの小信号ACモデルが示すように、最終段ミラー(電流ゲインBm(s))と駆動段(トランスコンダクタンスGd(s))の両方に、少なくとも1つの寄生極があります。

LDOの出力電流が減少するにしたがって、これらの寄生極は低い周波数に移動します。この原因は、ドレイン電流の減少に伴って各トランジスタのトランスコンダクタンスが低下する一方で、トランジスタの寄生静電容量がほぼ一定にとどまることにあります。

寄生極がレギュレーション・ループの位相マージンを低減させるのを防止するために、寄生極の周波数をレギュレーション・ループのUGFより高い値に維持できるように、LDOの出力電流が減少すると、駆動段のトランスコンダクタンスGd(s)は自動的に減少します。

この結果、UGFも同様に低くなり、寄生極の周波数との距離を維持します。このプロセスをUGFのアダプティブ調整と呼びます。

負荷のインピーダンスがZload(s)、レギュレーション・ループのゲインがFVFB(s)、レギュレーション・ループのUGFを上回る周波数帯で勾配が最大でも-30dB/decである場合、最小45°の位相マージンが得られます。

LDOの各ブロックの主要パラメータを表2に要約します。

表2のパラメータを使用すると、DC動的出力抵抗rOUT、および外部静電容量Cextが50nFの場合のレギュレーション・ループのUGFは、以下のように計算できます(両方とも、負荷電流50mAに対する代表値)。

比較のために、図11に示した駆動段と最終段ミラーの各単極モデルでは、カットオフ周波数がそれぞれ125.6MHzと26.1MHzとなっています。

(次回は11月2日の掲載予定です)

著者プロフィール

Pavel Horský (パヴェル・ホルスキー)オン・セミコンダクターの技術スタッフのメンバーで、専門分野はEMC、ESD、信頼性を重視した自動車用アナログ/ミクスド・シグナルIC設計。

1997年から、アルカテル・マイクロエレクトロニクス、AMIセミコンダクター、オン・セミコンダクターで、アナログおよびミクスドシグナル・デザインエンジニア、テクニカル・プロジェクト・リーダー、アナログASIC設計グループのリーダーを歴任。

チェコ共和国ブルノ工科大学で、1994年にラジオエレクトロニクス理学士号、1998年に計測学で博士号を取得。

2011年から同大学准教授として、博士課程の学生向けにアナログデザインコースを担当。60の出版物の著者および共同著者、15の米国特許の起草および共同起草者。

Libor Kadlčík (リボル・カドルーク)

オン・セミコンダクターのチェコ共和国にあるデザインセンターで、アナログASIC設計グループに所属。

チェコ共和国のブルノ工科大学で、2011年に電子通信学の理学士号、また2013年に理学修士号を取得。

現在、同大学の電子通信技術(D-EST)プログラムの博士号を取得中。