分数次数制御

提案したLDOの分数次数挙動は、誤差アンプ内にとどまります。その回路図を図9に示します。誤差アンプは、フィードバック抵抗性電圧分割器を通じて出力電圧をセンスします。実際の電圧とターゲット電圧の差は電流IFBで表現され、それに応じてアクション電圧VACTが調整されます。誤差アンプは、次のトランスインピーダンスを持つトランスインピーダンス・アンプに似た挙動を示します。

このトランスインピーダンスは、分数次数インピーダンスを近似します。

誤差アンプのトランスインピーダンスは、主に(左端を終端した有限)RCラダーによって設定されます。これはOTA(トランスコンダクタンス・オペアンプ)のトランスコンダクタンスがRCラダーのアドミッタンスを上回っているからです。例外は、OTAの寄生極が支配的になる非常に高い周波数帯です。

T型回路R1L0-R1L1-R1L2は、(ACT出力からOTAのFB入力までの間に)左側の終端抵抗と同等のトランスコンダクタンスを持ち、次式で表すことができます。

このT型回路は、このような大きい抵抗値を持つ抵抗を置き換えるので、占有チップ面積を削減することができます。

T型回路の仮想グラウンドは、電圧フォロワFLW100によって提供され、この電圧フォロワの公称出力DC抵抗RFLWは10.38kΩ(フォロワに接続された単一段アンプによっても満たすことができる値)です。

抵抗R1L0とR1L2の合成抵抗がLDOの電圧分割器が示す出力抵抗を上回るため、誤差アンプではフォロワの電圧オフセットに対する感度が低くなります。

RCラダーの設計にあたって、次数がα = 0.5、位相リップルがΔφfrac = 2.5(過度に長いラダーと、ワースト・ケースにおけるレギュレーション・ループの位相マージン劣化との間での妥協点)になるように、RCラダーのインピーダンスZfrac(s)を選択しました。参考文献[9]の数式(20)を使用すると、位相リップルに基づいて、次のとおり共通比の積が求まります。

この積を個別成分に分解します[9]。

等価左側終端抵抗R10Lは、次回説明する数式(16)と(17)にしたがい、電圧分割器のDCトランスコンダクタンスGv0に合わせて設計します。ここで、ZeFはRCラダーのシミュレーションから求めることができます。数式(6)を活用すると、最初の系列に当たるRC回路の抵抗R100は、次のようにR10Lから計算できます。

同時に、この回路の静電容量C100は、抵抗R100と同じレイアウト面積を占有するように選択します(同じカットオフ周波数を前提として、最小レイアウト面積を達成する組み合わせ)。他の抵抗と静電容量は数式(5)から計算します。これらを表1に要約します。

RCラダーを構成する抵抗とコンデンサの実際の値を表1に示します。これらはシミュレーション結果に基づいて、各素子の寄生静電容量を考慮に入れ、LDOに起因する互いに離れた複数の極を補償する目的で手動最適化を行った値です。

大きい値であるにもかかわらず、RCラダーの素子はアナログCMOS(相補型MOS)テクノロジで適切に実現できます。コンデンサはMOS構造の寄生静電容量で、抵抗はシリコン純物質ではないポリシリコン薄片です。

分数次数制御の使用法と様々な実装方法が参考文献[11]に掲載されています。

(次回は10月26日の掲載予定です)

参考文献

[9] VALSA, J., DVORAK, P., FRIEDL, M. Network Model of the CPE. Radioengineering, 2011, vol. 20, no. 3, p. 619–626. ISSN 1805-9600.

[10] PETRŽELA, J. Phase Shifters Using Passive Realizations of Fractal Capacitors (Posouvač fáze založené na využití pasivních realizací fraktálních kapacitorů). Slaboproudý obzor, 2014, no. 2, p. 6–12. ISSN 2336-5773. [11] PETRÁŠ, I. Fractional-Order Feedback Control of A DC Motor. Journal of Electrical Engineering, 2009, vol. 60, no. 3, p. 117–128. ISSN 1335-3632.

著者プロフィール

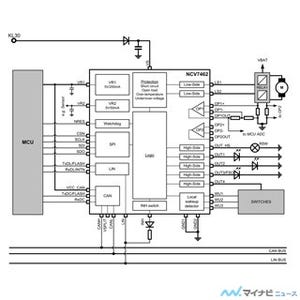

Pavel Horský (パヴェル・ホルスキー)オン・セミコンダクターの技術スタッフのメンバーで、専門分野はEMC、ESD、信頼性を重視した自動車用アナログ/ミクスド・シグナルIC設計。

1997年から、アルカテル・マイクロエレクトロニクス、AMIセミコンダクター、オン・セミコンダクターで、アナログおよびミクスドシグナル・デザインエンジニア、テクニカル・プロジェクト・リーダー、アナログASIC設計グループのリーダーを歴任。

チェコ共和国ブルノ工科大学で、1994年にラジオエレクトロニクス理学士号、1998年に計測学で博士号を取得。

2011年から同大学准教授として、博士課程の学生向けにアナログデザインコースを担当。60の出版物の著者および共同著者、15の米国特許の起草および共同起草者。

Libor Kadlčík (リボル・カドルーク)

オン・セミコンダクターのチェコ共和国にあるデザインセンターで、アナログASIC設計グループに所属。

チェコ共和国のブルノ工科大学で、2011年に電子通信学の理学士号、また2013年に理学修士号を取得。

現在、同大学の電子通信技術(D-EST)プログラムの博士号を取得中。