はじめに

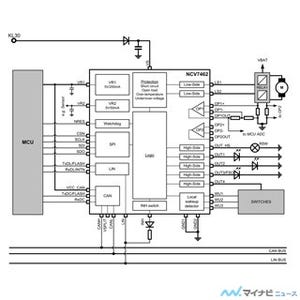

この連載では、オン・セミコンダクターの車載環境でも動作可能な5V、50mAの低ドロップアウト電圧レギュレータ(LDO)について説明します。このLDOは自身のレギュレーション・ループで分数次数制御を使用して、(厳密なDCレギュレーションのために)高いDCゲインを達成すると同時に、(良好な安定性のために)高周波での高ゲインを防止します。補償ゼロは必要ありません。また、レギュレーション・ループのユニティ・ゲイン周波数により、出力電流に応じてアダプティブに変化し、非支配極よりも低い周波数に維持することが可能です。

まず最初に、従来型LDOの概念、DCレギュレーション誤差とレギュレーション・ループ安定性間のトレードオフ、および分数次数制御方式でこれらの課題を解決する方法を示したいと思います。

従来型LDOの概念

低ドロップアウト電圧レギュレータ(LDO)は、電源(入力)電圧が出力電圧に非常に近い場合でも、ほぼ一定の出力電圧を維持できるリニア電圧レギュレータです。LDOはリニア電圧レギュレータの中で最も一般的な分類の1つです[1][2][3][4][5][6]。

図1にLDOトポロジの原理を示します。出力電圧を希望の値(REFピンの基準電圧に応じた値)に維持するために、コントローラgm1は抵抗を組み合わせた電圧分割器R3-R4を使用して出力電圧(OUTピン)を監視し、最終段トランジスタM2のゲートを制御して、入力(INピン)から出力に供給される電流を設定します。

結果として得られるレギュレーション・ループは負であり、2つの極が存在します。1つは内側の極(RC回路R1-C1によって形成)、もう1つは外側の極(負荷の静電容量C2と、負荷抵抗R2と電圧分割器の抵抗R3-R4との並列合成抵抗、およびトランジスタM2の動的出力抵抗によって形成)です。

一般的に、どちらの極が支配的か非支配的かに応じて、3種類のLDOの概念に分類できます。支配極はレギュレーション・ループのUGF(ユニティ・ゲイン周波数)を設定し、非支配極は小さく周波数を設定しますが、後者の周波数はUGFより高いことが望まれます。

最初の概念は、内側の極と外側の極の両方が支配的な場合です。レギュレーション・ループの開ループ・ゲインは-40dB/decという勾配になります。レギュレーション・ループの安定性を受け入れ可能な水準にするには、勾配を緩和するために補償ゼロ(周波数はUGF以下かその付近)が必要です。この利点は、内側の支配極が(ほぼ)統合的なレギュレーションを実現することを暗黙で意味し、結果としてDCレギュレーション誤差が非常に小さくなることです。

2番目の概念は、内側の極が非支配的、外側の極が支配的な場合です。負荷の静電容量は特定の値を上回っている必要があります。結果として生じる寄生ゼロがUGFに影響を及ぼさないように、通常は負荷のESRとESL(等価直列抵抗と等価直列インダクタンス)が制限されます。利点は、最大負荷静電容量が制限されず、そのESRが0であってもよいことです(負荷電流過渡に対する応答を改善するため)。比例レギュレーションと、非ゼロDCレギュレーション誤差の関係は、非支配的な内側の極によって暗黙的に制御されます。

3番目の概念は、内側の極が支配的で、外側の極が非支配的な場合です。外側の極が非支配的なので、必然的に外側の極は高い周波数へと押しやられ(この概念は、最終段トランジスタM2が電圧フォロワである場合に最適)、多くの場合は上限が負荷静電容量C2に依存する形になります。この場合の利点は、DCレギュレーション誤差が非常に小さくなることです。

最初の概念が広く採用されています。DCレギュレーション誤差が小さく、補償ゼロを形成する多くの方法が文献に掲載されているからです。参考文献[1]の図4では、電流制御の電流源によってゼロが形成されます。参考文献[2]の図1では、外付けコンデンサのESRと、コンデンサCf2によってゼロが形成されます。参考文献[3]の図5では、電流アンプとコンデンサCfで構成される並列信号パスでゼロを形成しています。参考文献[4]では、CFAの接続部からLDOの出力に至る並列信号パスが構成されます。参考文献[5]では、並列信号パスはコンデンサCcに到達します。参考文献[6]の図5では、出力バッファの補償ゼロは、内側のオンチップ出力コンデンサのESRによって形成されます。

この連載では図2に示すLDOトポロジに注目しています。このトポロジは、最初の概念と2番目の概念に適しています。このトポロジは最終段の電流ミラーM1-M2によって構成され、電圧分割器R1-R2とトランスコンダクタ(トランスコンダクタンスがGe(s)である誤差アンプ)で構成されるコントローラがこのミラーを駆動します。

厳密なDCレギュレーションを実現できるようにレギュレーション・ループのDCゲインを大きくする必要があり、寄生極(またはゼロ)がループの安定性に影響しないように、ループのUGFを過度に高くしないことも求められます。

1つの寄生極であるPmは、トランジスタM1のトランスコンダクタンスと、最終段ミラーのゲート静電容量Cpmで形成されます。外付けコンデンサCextのESR (RESRext)によって生じたゼロが、1つのゼロになる可能性があります。

外側の支配極Poutは、外部静電容量Cextによって出力端子(OUT)の位置に形成され、レギュレーション・ループの開ループ・ゲインの勾配が最大-20dB/decだけ増大します。

用語「出力電流」IOUT(s)は、出力ピン(OUT)から引き出される電流のみ暗黙的に意味するのに対し、「負荷電流」Iload(s)は、外部コンデンサCextから供給される電流も含むことに注意してください。

コントローラの伝達関数Gc(s)を選択するアプローチは複数存在します。

最初のアプローチは、最初のLDO概念を実装し、コントローラを1次積分器として使用します。この場合の利点は、DCレギュレーション誤差が非常に小さくなることです。レギュレーション・ループの開ループ・ゲイン(VFB、電圧フィードバック)は、図3の特性(a)に示すように、-40dB/decの勾配に達します。欠点は、レギュレーション・ループの安定性を維持するために、補償ゼロZcompを用意して、ループのUGF周辺で勾配を低減する必要が生じることです。

2番目のアプローチは2番目のLDO概念を実装し、(UGF以下およびUGF付近で、周波数に依存しないトランスコンダクタンスを使用して)コントローラを比例システムとして使用します。レギュレーション・ループには1つの支配極(Pout)があります。他極(Pmなど)は非支配的であり、これらの非支配極がレギュレーション・ループの安定性を悪化させないように、図3の特性(b)で示すような周波数特性にする必要があります。欠点は、厳密なDCレギュレーションを実現しようとすると、UGFを高くするための変更が必要になり、良好な安定性の実現が困難になることです。

上記のアプローチでは、DCレギュレーション誤差を小さくしようとすると、必然的にUGFを高くするか、補償ゼロを設けることが求められます。

(次回は10月5日の掲載予定です)

参考文献

[1] CHAVA, C.K. – SILVA-MARTINEZ, J. A frequency compensation scheme for LDO voltage regulators. IEEE transactions on circuits and systems I: regular papers, 2004, vol. 51, no. 6, p. 1041–1050. DOI: 10.1109/TCSI.2004.829239.

[2] KA NANG LEUNG, MOK, P.K.T., ASI IT LAU. A low-voltage CMOS low-dropout regulator with enhanced loop response. Proceedings of the 2004 International Symposium on Circuits and Systems, 2004. ISCAS '04, 2014, vol. 1, p. 385–388. DOI: 10.1109/ISCAS.2004.1328212.

[3] MILLIKEN, R.J., SILVA-MARTINEZ, J., SANCHEZ-SINENCIO, E. Full On-Chip CMOS Low-Dropout Voltage Regulator. IEEE Transactions on Circuits and Systems I: Regular Papers, 2007, vol. 54, no. 9, p. 1879–1890. DOI: 10.1109/TCSI.2007.902615.

[4] WONSEOK OH, BAKKALOGLU, B. A CMOS Low-Dropout Regulator With Current-Mode Feedback Buffer Amplifier. IEEE Transactions on Circuits and Systems II: Express Briefs, 2007, vol. 54, no. 10, p. 922 – 926. DOI: 10.1109/TCSII.2007.901621.

[5] AL-SHYOUKH, M., HOI LEE, PEREZ, R., A Transient-Enhanced Low-Quiescent Current Low-Dropout Regulator With Buffer Impedance Attenuation. IEEE Journal of Solid-State Circuits, 2007, vol. 42, no. 8, pp. 1732–1742. DOI: 10.1109/JSSC.2007.900281.

[6] HAZUCHA, P., KARNIK, T., BLOECHEL, B.A., PARSONS, C., FINAN, D., BORKAR, S. Area-Efficient Linear Regulator With Ultra-Fast Load Regulation. IEEE Journal of Solid-State Circuits, 2005, vol. 40, no. 4, p. 933 – 940. DOI: 10.1109/JSSC.2004.842831.

著者プロフィール

Pavel Horský (パヴェル・ホルスキー)オン・セミコンダクターの技術スタッフのメンバーで、専門分野はEMC、ESD、信頼性を重視した自動車用アナログ/ミクスド・シグナルIC設計。

1997年から、アルカテル・マイクロエレクトロニクス、AMIセミコンダクター、オン・セミコンダクターで、アナログおよびミクスドシグナル・デザインエンジニア、テクニカル・プロジェクト・リーダー、アナログASIC設計グループのリーダーを歴任。

チェコ共和国ブルノ工科大学で、1994年にラジオエレクトロニクス理学士号、1998年に計測学で博士号を取得。

2011年から同大学准教授として、博士課程の学生向けにアナログデザインコースを担当。60の出版物の著者および共同著者、15の米国特許の起草および共同起草者。

Libor Kadlčík (リボル・カドルーク)

オン・セミコンダクターのチェコ共和国にあるデザインセンターで、アナログASIC設計グループに所属。

チェコ共和国のブルノ工科大学で、2011年に電子通信学の理学士号、また2013年に理学修士号を取得。

現在、同大学の電子通信技術(D-EST)プログラムの博士号を取得中。