ベルギーimecの年次イベント「ITF World 2023」にて、「Chat GPT」に代表されるような生成AIの一般社会に与える影響などが話題として取り上げられ、多くの講演者が、今後の半導体産業の成長ドライバーとして生成AIに言及した。

NVIDIAのJensen Huang CEOは「ChatGPTは革命だ」と語ったほか、imecのLuc Van den hove CEOは、「生成AIは現代のビッグバンだ」と述べていた。また、AMDの上級副社長兼CTO(最高技術責任者)のMark Papermaster氏は、生成AIによるデータの爆発的増加に伴い電力も爆発的に消費される問題に言及し、異種チップ集積(ヘテロジニアスインテグレーション)などの半導体技術によってデータセンターの消費電力を1/30に削減する計画について説明した。

2Dの微細化と3D積層化で半導体の集積度向上は継続

生成AIを「現代のビックバン」だと主張するVan den hove氏は「AIを支えるデバイスの計算能力や取り扱うデータ量は爆発的に増えていく。我々は現在、その初期の段階にいるといえる。今後はデータセンターが担う情報処理能力が飛躍的に増加していく。既存のデバイスやシステムはこれからのAIニーズに対応するために劇的な変化が求められる」と述べた(図1)。

また、デバイスやシステムの性能を上げるための高集積化はどのように実現していくかという点については、「ここ数十年に渡りムーアの法則に従い2次元での微細化によりデバイスの集積度は向上してきた。imecでも今後もこの方向性でムーアの法則を延命・継続させることに注力していく」と述べたほか、今後は3次元スタッキング(積層)で集積度を向上させていくことにも注力し、両面でデバイスの集積度を向上させていく方向性を示した。

2次元のプロセス微細化に威力を発揮するのが2019年の7nmプロセスより量産導入されたEUV露光技術であり、今後はさらなる解像度向上が可能な高NA EUV露光装置(NA=0.55)の実用化に期待がかかる。imecは、ASMLと共同でオランダに「High-NA Lab」を設立し、高NA EUV露光技術の実用化を促進しようとしている。

微細化に頼らない集積度向上技術も模索

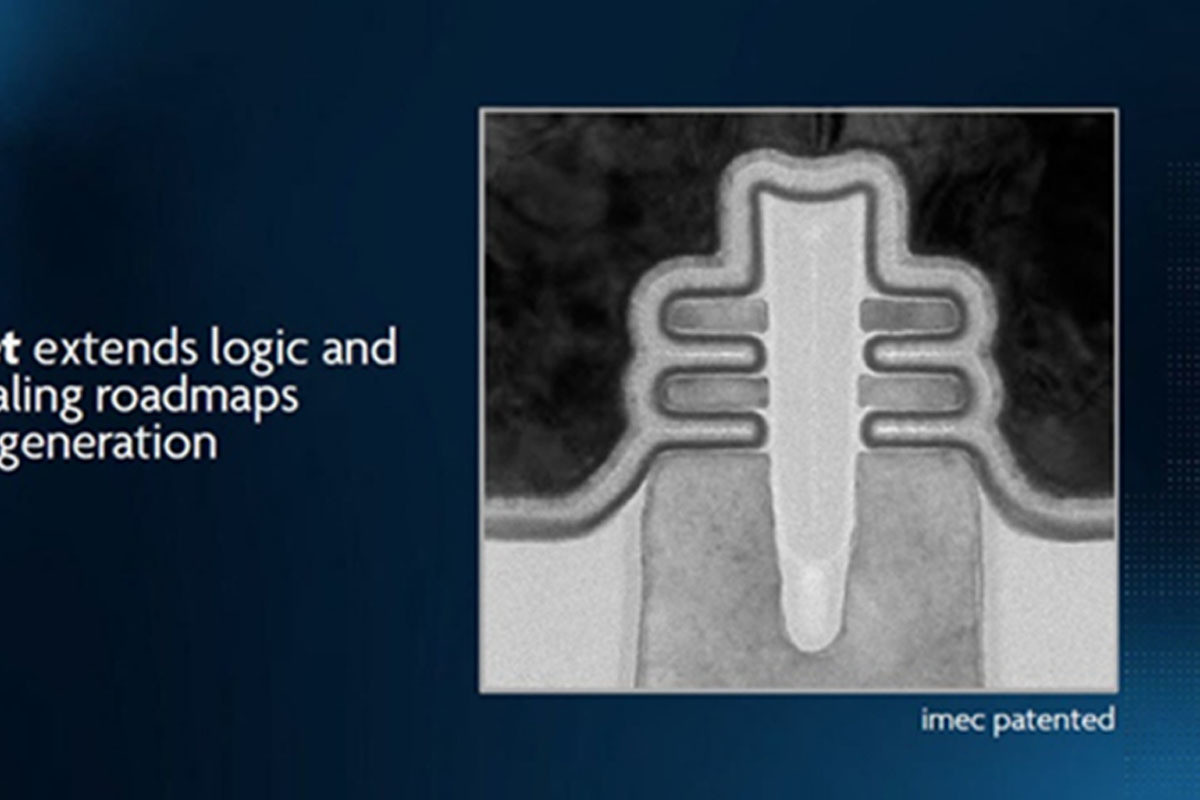

また、imecは、トランジスタ構造の進化についても現在主流のFin-FETからナノシートを用いたGate-all-around(GAA)FET、フォークシートを用いたGAA FETを経てCFET(Complementary FET)に至るロードマップをすでに示している。究極のトランジスタ構造と言われるCFETはp型MOSFETの直上にn型MOSFETを積層した構造で、CMOSの専有面積を最小化できる(図3)。

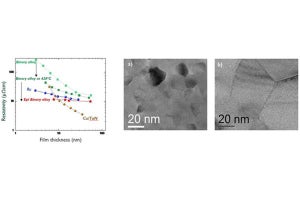

このほか、裏面電源供給網(BSPDN)にもめどをつけて、表面の多層配線網を裏面に移動し、表面のトランジスタ密度を上げる手法やチャネル移動度向上のための2D材料(半導体単層遷移金属ジカルコゲナイド)をチャネルに採用する研究にも見通しが得られつつあり、図2に示すような2036年に至る微細化ロードマップの公表に至った。 一方、プロセスの微細化によらない集積度向上策として3次元積層にも注力しており、技術プロセスのまったく異なる異種デバイスの積層、いわゆる「ヘテロジニアスインテグレーション」を実現するという(図4)。図4は、2032年ごろの最先端微細プロセスによるA5ロジック回路から2012年ごろ主流だったマチュアプロセスによる28nm I/O回路まで、さまざまな微細化プロセスによる集積回路を3D IC化した例を示したもので、組み合わせたデバイスを相互に結合させるために、TSV(シリコン貫通ビア)、Cu-Cu接合、D2Wマイクロバンプなどさまざまな実装技術を導入する必要があるとしている。