ITF World 2024にてIntelのSVP兼技術開発および外部研究開発契約担当ゼネラルマネージャーのSanjay Natarajan氏は、Inte Foundryの立場で「ムーアの法則を継続させるための半導体研究」と題した講演を行った。

まだまだ続くムーアの法則

Intel共同創業者のGordon Moore氏が前身のFairchild Semiconductor勤務時代に提案した、いわゆる「ムーアの法則」はその後50年以上にわたり生き続け、半導体産業発展の礎となってきた。Intelは、この法則を将来にわたって継続させるために先端半導体の研究開発に取り組んでいるとNatarajan氏は強調した。

-

ムーアの法則のもととなった原典は同氏がFairchild勤務時代に電子技術誌「Electronics」へ寄稿した記事。集積回路の搭載素子数が将来的に増加していくというものだが、その後、半導体産業は同氏のこの提言通りに50年以上にわたってトランジスタ数を増加させてきたと言える (出所:Intel)

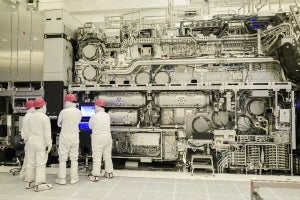

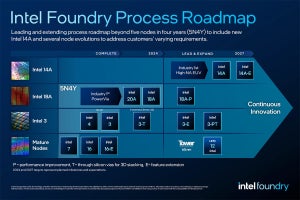

Intelは、過去数十年にわたってムーアの法則に沿って、一歩一歩着実に微細化・高集積化を進めてきており、現在はIntel 18A(いわゆる1.8nmプロセス)での生産に向けた開発が最終段階にある。また、すでに高NA(NA=0.55)のEUV露光装置を米国オレゴン州の試作ラインに導入しており、次世代となるIntel 14A(いわゆる1.4nmプロセス、あるいは14Å)の開発を開始。さらにその先の微細プロセスの開発も視野に入れているとする。

ムーアの法則の維持に必須のトランジスタ構造の変化

さまざまな電子機器から生成されるデータの総量は指数巻子的に増加しており、ペタからエクサ、そして2030年にはゼタレベルに達することが見込まれている。AIの普及によって、さらに高性能な演算能力が求められるようになってきており、Intelはそうした市場からの要求に応えるべくHPCの研究開発を強化しているという。

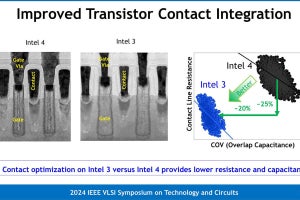

HPCを中心に、高性能な演算能力を提供するべくトランジスタ構造の変化が進んでいるが、その適用プロセスのライフサイクルは徐々に短くなってきている。

旧来のプレーナー構造がFinFETに替わるのには30年以上の時間を必要としたほか、RibonFET(これはIntel用語で一般にはGate-All-Around(GAA)FET)に替わるのに約15年ほどの時間を必要とした。しかし、10年後にはStacked RibbonFET(これもIntel用語で、imecではCFETと呼んでいる)に替わることが予想されている。その先については、不透明な状況で確実な見通しは出せないが、現在、2DチャネルFET、Magnetro Electric Spin Orbit(磁電気スピン起動デバイス)、Fe(強誘電体ゲート絶縁膜)FETなどが提案されているとする。

また今後についてはトランジスタ構造のみならず、裏面電源供給のためのパワービア技術や3次元パッケージング技術もムーアの法則を継続させるのに役立つ技術となるともしている。

さらに同氏は、従来のプロセス技術-デバイス同時最適化(Technology-Device Co-Optimization:TDCO)をさらに拡張して、プロセス技術からパッケージング技術、システムアーキテクチャ、ソフトウエア、デバイス応用までを同時最適化するシステム-プロセス技術同時最適化(System Technology Co-Optimization:STCO)がムーアの法則の先導役を果たすものとなるとの見方を示す。

バイポーラからCMOS へ、そしてその先は?

バイポーラトランジスタを高集積化するにつれて、消費電力が急増したため、1990年代に低消費電力が特徴のCMOSに置き換わった。しかし、そのCMOSも近年の高集積、高性能化で消費電力が増加してきており、Beyond CMOSの登場に期待がかかる。しかし、Beyond CMOSがどのようなものかはまだ良く分かっておらず、CMOSを置き替えるというよりは、CMOSを補強する役割を演ずる可能性が高いと同氏は指摘する。

そのため、今後Beyond CMOS分野の研究をさらに活発に行う必要があるとしており、Intelもimecのコアプログラムメンバーの一員として研究協業を推進し、ムーアの法則のさらなる継続に向けた革新的な研究にまい進するとしている。