Knights Landingコア

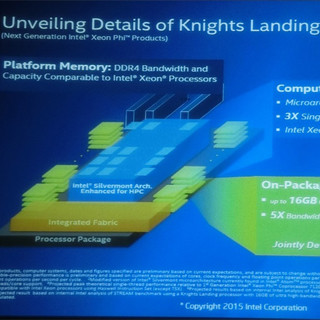

KNLのコアは、Atomに使われているSilvermontコアをベースにしているが、次の図にリストされているように多くの改良が加えられている。そして、2個のコアとそれらで共有される1MBのL2キャッシュ、メッシュインタコネクトを構成するHUBからなるタイルを単位として構成されている。

KNLのコアは2命令のOut-of-Order実行をサポートし、4スレッドを並列実行するように拡張されている。KNCでは2スレッドを実行しないと実行パイプラインをフルに使用することができなかったが、KNLでは、1スレッドしか実行していない状態でも実行パイプラインをフルに使用でき、最大性能を達成できるとのことである。

そして、KNLコアは、最大72命令を仕掛中(In Flight)として実行を行うことができる。Out-of-Orderの並列度やIn Flightの命令数はXeon CPUコアと比べると半分程度であるが、メニーコアチップのプロセサとしては妥当なバランスと思われる。また、命令、データそれぞれ32KBの1次キャッシュを持ち、Dキャッシュは2個の64バイトのロードポートを備え、2つのロードを並列に処理できるようになっている。

さらに、TLBサイズの拡大、L1キャッシュとL2キャッシュのプリフェッチャーの装備、アラインされていないアドレス、キャッシュラインをまたがるメモリアクセスの高速化、Gather/Scatterの高速化、Silvermontコアと比べてDキャッシュとL2キャッシュ間のバンド幅の倍増などの改良が加えられている。そして、各コアは512bit幅のVPU(Vector Processing Unit)を2個持ち、単精度(SP)では32演算、倍精度(DP)では16演算を並列に実行することができる。

KNLチップは72コアを搭載しているので、1サイクルに最大1152DP積和演算を実行できる。これで3TFlopsを達成するためには、積和演算は2Flopと計算するのでKNLのクロックは1.3GHzという計算になる。また、性能は3+TFlopsという表現になっているので、ターボ時かもしれないが、これよりもクロック周波数は高くなる。

また、KNLのタイルは2コアを含んでいるので、72コアということは36タイルである。ということは、4×9タイルという可能性は皆無ではないが、まあ、6×6タイルの配置で、これらのタイルをメッシュインタコネクトで接続していると考えられる。

なお、チップには72コアが搭載されるが、歩留まり改善のため、当初は、いくつかの不良コアを許容してより少ないコア数で商品化される可能性もある。

KNLの命令セットは、原則、Xeon CPUと同じである。これはXeon CPUのバイナリはそのままで動くが、前世代のKNCのコードは、再コンパイルしないと動作しないということを意味している。

Xeonとの命令互換であるが、x87命令、MMX、SSEなどのレガシー命令やビット操作命令などは互換であるが、トランザクション処理用のTSX命令はKNLではサポートされていない。

一方、AVX512命令に関しては、マスク付きのベクトル拡張命令、新しいプリフェッチ命令、新規の指数関数や逆数命令、ベクトル化の障害の検出命令などはKNLではサポートされているが、Xeon CPUではサポートされていないという違いがある。

次の表に、AVX512の拡張命令を示す。VPCONFLICT命令はベクトルの中で重複した値(依存関係がありベクトル実行できないという意味か?)を検出し、ベクトル化に支障のないサブセットを作ると書かれており、ベクトル化できる部分はベクトル化し、そうでない部分は、後で、スカラで実行するための機能と思われるが詳細は不明である。