半導体は、近年のあらゆる技術転換点の根幹をなしている。PC時代は強力なマイクロプロセッサの登場で幕を開けた。モバイル時代を牽引したのはスマートフォンに搭載された高性能・省電力チップであり、クラウド時代は大規模データセンター内に設置されたプロセッサや大量のメモリやストレージが主導している。

これらの市場が今もかなりの規模を保って成長を続ける一方、IoT、ビッグデータ、5Gを柱とするAI時代が到来し、斬新なコンピューティングアーキテクチャとチップデザインによって形作られている。

半導体技術の進歩は、今やグローバル経済の成長に不可欠な要素となっている。この新時代には、高性能のロジックとメモリを大量に供給する必要が出てくる。半導体技術のロードマップがもしこれに見合うペースで前進できないとしたら、その代償はきわめて大きいだろう。

新しい技術ノードを研究開発から量産にまで導くプロセスはきわめて複雑で、欠陥を検出・修正する能力に大きく依存する。ところが、業界で欠陥検査とレビューに用いられている手法は数十年来あまり変わっていない。そろそろ見直しの時期が来ているようだ。

これから数回シリーズで、欠陥検出・修正の技術課題について考察していきたい。

半導体業界の進歩を妨げる要素は、グローバルなエレクトロニクス業界のエコシステムに大きな波紋をもたらすのが常であり、そうした障害を早く克服するほど世界の発展は迅速に進む。これは時間との闘いなのだ。

時は金なり

半導体事業は巨額のコストを伴うので、時間の短縮がビジネスにおいて非常に重要になる。したがって、開発期間、量産までの期間、市場投入までの期間、収益実現までの期間の短縮は必須となる。

中でも最も重要なパラメーターは、歩留まり確保までの期間(time to yield)だ。新プロセスの研究開発から生産立ち上げを経て量産に至るまでの期間をわずかでも短縮できれば、半導体メーカーには数十億ドル規模のメリットが生じるのである。

もちろんその逆も成り立つ。歩留まり改善に遅れが出れば、世界の中でも最も価値のあるビジネスを支えるコンピューティング新時代における時間とコスト、市場シェアのロスが生じることとなる。

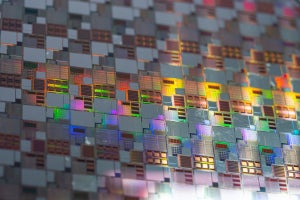

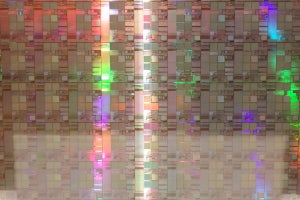

複雑化するチップ構造

欠陥検出は、歩留まり改善を左右する主要因である。歩留まり低下をもたらす欠陥の発見が早ければ早いほど修正も迅速に行える。しかし、欠陥の検出は難しさを増しつつある。たとえば線幅の微細化が進んだ結果、それまで致命的ではなかったわずかなニューサンス欠陥(Nuisance defect、従来は欠陥ではなかったもの)も歩留まりキラーになり得る。あるいは、精緻な3Dトランジスタの構築で複雑なマルチパターンステップを形成する際、わずかなばらつきが増幅されて歩留まりを損なう欠陥につながる場合もある。

こうしたケースでは、欠陥が発見されるのが原因発生のかなり後になる場合が多く、欠陥の発生後に実施されるプロセスはすべて時間とコストの無駄になってしまう。

チップ構造の複雑化が進み、欠陥検出が困難の度を増しているなか、業界は本来ならば検査回数を増やすべきだが、実際には逆に検査ステップに制限がかけられつつある。なぜだろうか?

経済性の課題

ここで問題となるのが、ファブの経済モデルだ。

微細化が1nm進むごとに、ウェハ処理ステップの数は大幅に増加する。検査ステップが増えればコストも増える。また欠陥を探すために用いる光学検査装置も高度化が進んでいるため、そのコストも上昇している。

検査装置のコストが増えれば、1ウェハに対するスキャン当たりのコストも上昇する。

その結果、こうしたプロセスコントロールのコスト膨張を抑制するため、技術者たちは検査すべきステップの数をやむなく減らしている。当然のことながら、検査ステップ数を減らせば取得できるデータ数も減るため、欠陥の検出、トレース、主因分析、修正を早めるのが難しくなり、歩留まり確保までの期間短縮も難しくなる。とはいえ、検査にコストがかかるのは厳然たる事実で、いくら祈ってもコストはなくならない。

プロセスレシピに組み込む検査ステップ数を減らすことは、数少ないコスト抑制手段の1つなのだ。ファブが検査に割り当てる予算は限られているため、技術者たちはその制約内でできるだけ多くのデータを収集して、後は成り行きに任せるしかない。

現行の検査パラダイムは、今とはまるで違う状況下で生まれたものだ。当時ムーアの法則はまだ健在で、ニューサンス欠陥もウェハマップ上でとるに足りないものだったが、今ではそうした欠陥も歩留まりキラーになり得る。現実には、業界が実施している検査ステップの数も収集されるデータも、チップ構造の複雑化に照らすと相対的に十分とは言いがたい。本来なら逆に検査を増やすべきところである。

今必要なのは、プロセスコントロールの新しいプレイブックを導入し、ファブの経済性を維持しながら歩留まり確保までの期間を短縮することだ。これが半導体業界において必要不可欠なイノベーションといえよう。

次回はAI時代の欠陥検出・修正に革命をもたらすブレークスルーについて述べる予定だ。

この連載はApplied Materialsが発行している英文ブログをアプライド マテリアルズ ジャパンが翻訳したものを一部修正して掲載しております。

著者プロフィール

Ortal YesodiApplied Materials

プロセス ダイアグノスティックス&コントロール、オプティカルディフェクトコントロール部

プロダクト マーケティング マネージャー

2013年Applied Materials入社。

イスラエルのネゲヴ・ベン=グリオン大学で電気・コンピュータ工学の学士号取得