今までに得られたESDに関する5つの知見

imecでは、今までの研究や調査で、ESDに関して以下の5つの知見を得ている。

1. 電圧抑制効果によりESD保護回路の必要性が低減

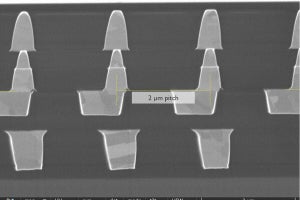

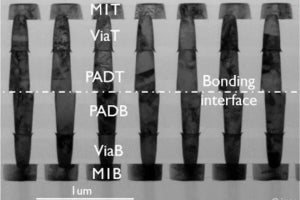

内部I/OピンにESD保護回路がない場合、非常に低いESD電圧でも敏感な内部I/O回路が破損する可能性がある。幸いなことに、ボンディングステップでは、電圧抑制効果という重要な効果が有利に働く。ダイ・ツー・ウェハまたはウェハ・ツー・ウェハのボンディング中、ダイ/ウェハとターゲットウェハは平行板コンデンサーと見なすことができる。物理法則に従い、ダイ/ウェハがターゲットウェハに近づくと間隔が狭まるため、その静電容量が増加する。これにより、脅威となる静電電圧が大幅に減少する。

imecの研究者は、簡素化されたハイブリッドボンディング実験セットアップでこの効果を確認した。測定結果によると、この効果は、ダイ・ツー・ウェハボンディング構成よりもウェハ対ウェハボンディングの方がはるかに顕著である。予備的な結果では、ウェハ・ツー・ウェハボンディングではESD保護が不要である可能性があることが示唆されているが、実際のボンディングプロセスでこの効果がどの程度強くなるかを調べるには、さらなる研究が必要である。

-

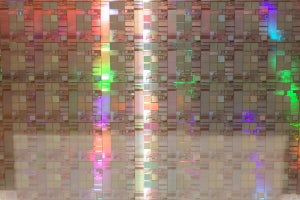

(左)ダイとウェハのハイブリッド接合の電圧抑制効果を調査するための実験セットアップの概略図。ハイブリッド接合チップとウェハを表すために金属プレートを使用。(右)ハイブリッドスタッキング中のさまざまな間隔での電圧と静電容量の測定。2024 VLSI Symposiumで発表された (出所:imec)

2. ボンディングツール開発者への呼びかけ:ボンディングツール内にESD防止機能を導入

上記の実験からわかるように、電圧抑制効果の有効性にはいくつかの要因が影響している。その1つは、ダイまたはウェハホルダーからの寄生容量である。これは、ホルダーからの寄生容量を最小限に抑えるなど、ボンディングツール自体がESD防止に重要な役割を果たすことができることを示している。もう1つの例は、ダイ対ウェハアセンブリツールにカスタム空気イオン化ソリューションを組み込むことである。これにより、ツール内でダイを安全に放電することができる。

3. ESD保護回路を設計する際には、保護回路からの直列抵抗を考慮する必要

外部ESD制御対策で完全に破壊を防止できない場合は、ESD電流を排出するために内部ESD保護回路が不可欠である。前述のように、これらの回路に使用できるスペースは限られている。しかし、いくつかのことを考慮することにより、過剰設計を回避し、面積の消費を減らし、内部I/O回路のパフォーマンスを維持することができる。

imecの研究チームは、ESDイベントが保護回路に到達した後のESDパルス形状を分析した。チームは、ESDパルスの立ち上がり時間が速い(22ps)ことを観察した。これは、一般的なCDMパルスよりもはるかに高速である。さらに、相互接続金属線とESD保護デバイス自体から生じる直列抵抗は、ESDパルス形状に大きな影響を与える。たとえば、直列抵抗が高い細い相互接続線は、ESDパルス形状にプラスの影響を与える傾向があり、CDM放電が遅くなり、ピーク電流が小さくなる。

これらの観察結果は、2.5/3DテクノロジのESD保護回路を設計する際に、ESDパルスの特性と回路の直列抵抗を無視できないことを示している。考慮しないと、過剰なESD保護につながり、Si領域の不要な使用と内部I/Oピンのパフォーマンス低下につながる可能性がある。一方、可能な場合は直列抵抗を増やすと、必要なESD保護回路のサイズが小さくなる。

4. 3D SoCにはESD保護に対するカスタマイズされたアプローチが必要

電圧抑制効果により、最終的にはウェハ対ウェハ接合構成のI/OインタフェースにESD保護回路を実装する必要がなくなる可能性があることはすでに述べた。ESD保護の必要性がさらに高まるダイ対ウェハ接合プロセスの場合、imecの測定結果では、ダイのサイズもESDイベントの発生/範囲に重要な役割を果たすことが示されている。したがって、ダイのサイズは保護回路の設計においても重要な要素となる。

全体的に、3D SoCでは、ESD保護に対してカスタマイズされたアプローチが必要である。異なるボンディングテクノロジ、およびダイ・ツー・ウェハボンディングの場合は異なるダイサイズに対して、異なる設計戦略が必要です。ダイ・ツー・ウェハとウェハ ・ツー・ ウェハの両方のテクノロジについて、マイクロバンプとハイブリッドボンディングアプローチの特定のニーズを調査するには、さらに研究が必要である。

5. 新たな基準の必要性を確認

ベアチップおよびウェハのI/OインタフェースでESDイベントが発生すると、パッケージ化されたチップ用に書かれた従来の標準の制約内で想定されるものとは異なる動作をESDパルスが行うことが観察される。imecの測定により、テストの要件を定義する新しい標準を開発する必要があることが確認された。

結論と展望

さまざまな2.5D/3Dテクノロジによって提供される相互接続密度の継続的なスケーリングにより、スタッキング中の内部I/OインタフェースのESD保護が課題となっている。将来の3D SoCでは、ESD保護回路を実装するためのスペースがほとんどなくなるため、ESD防止にさらに多額の投資が必要になる。

保護回路が依然として必要な場合は、保護回路の過剰設計を回避するのに役立ついくつかの設計要素を検討できる。全体として、3D相互接続テクノロジごとに、ESD保護と防止に対する異なるアプローチが必要になる可能性がある。imecはESD協会と緊密に協力し、3D固有のESD保護戦略の開発に向けた研究を続けている。長期的には、この共同作業により、高度な2.5/3D技術のESD堅牢性をテストおよび認定するための新しい標準が生まれることが期待される。

|

|

Shih-Hsiang (Shane) Lin

2018年に台湾の高雄にある国立高雄大学(NUK)で電気工学の学士号を取得したのち、2021年に台湾の台南にある国立成功大学(NCKU)で修士号を取得。さらに、2021年にはimecで1年間インターンとして働いた。2021年にブリュッセル自由大学(VUB)の電子情報学部(ETRO)博士課程に入学。同時に。ベルギーのimecの静電放電(ESD)チームに加わり、博士号取得を目指している。現在の研究テーマは、3次元(3D)技術におけるESDリスク調査である。 |

|

|

Marko Simicic

クロアチアのザグレブ大学で、2010年に電気工学、2012年に情報技術の理学士号、修士号を取得。2018年にベルギーのルーヴェン・カトリック大学(KU Leuven)工学部電気工学科で博士号を取得。2017年にベルギーのimecのESDチームに加わり、2022年から認定ESD制御プログラムマネージャーを務めている。国際ジャーナルや会議の議事録で35本以上の論文を執筆している。現在の研究分野はかなり幅広く、先進半導体や3D/2.5Dスタッキング技術におけるESDデバイスと回路の設計、新しいESDテスト、ESD制御プロセス評価などを行っている。 |

|

|

Nicolas Pantono

imecの主任技術者。2010年にベルギーのブリュッセル大学で電気工学の学士号、2012年に修士号を取得。2021年に、ベルギーのKU Leuvenの電気工学科で博士号を取得。さらに、2015年にはベルギーのSolvay Business Schoolで経営管理と財務の修士号を取得。2013年に、imecの3Dおよびシリコンフォトニクス部門に加わった。彼の研究は、モバイル、高性能コンピューティング、AI、自動車などのアプリケーション向けの2.5D/3D統合システムの電気および光相互接続に焦点を当てている。 |