セルライブラリの専有面積削減で微細化

微細化は、EUVリソグラフィの導入といった製造技術の革新だけではなく、設計上の工夫によってももたらされる。セルライブラリのトラック数を減少させ、セルの高さを低めてセル専有面積を縮小する手法である。

図1は、前回も示したimecの高性能ロジックICのトランジスタの微細化に向けたロードマップであるが、この図の中央上部に「標準セルライブラリのトラック高の低減(7.5トラックから3トラックへ)、FinFET搭載数の削減」という記述がある。これについて詳しく説明しよう。

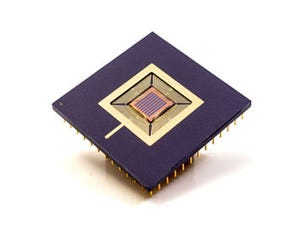

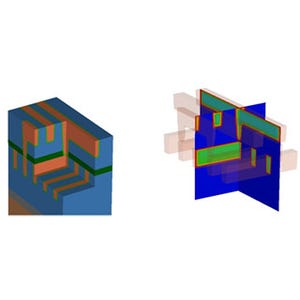

現在、半導体の最先端量産プロセスとなる10nmプロセスに採用されているセルライブラリは、7.5トラックで、そこに搭載されるFinFET当たりのフィン(図2で緑色の棒で表現されている)の数は3である。赤色の棒の幅がゲート長、ゲートピッチは64nm、メタルピッチは48nmである。

10nm以降においては、技術ノードごとにセル専有面積を半減させていき、5nm技術ノードでは、6トラック(FinFETのフィン数は2)、3nmでは、4トラックとなるが、FinFET当たりフィン数は1になってしまう。2nmでも同様である。フィン数が減ってしまうと駆動電流が減ってしまい性能低下をきたすので、このデメリットを補うために、図2下部に断面SEM写真で掲載されているような、いくつかの要素技術(自己整合ゲートコンタクト、2層ではなく3層のメタル層を接続するスーパービア、スペースを節約するための電源レール埋め込み、相補型FETなど)を開発中であるという。

もし、何らかの事情でEUVリソグラフィが量産適用できず、ArF液浸リソグラフィを継続して使用することになった場合には、上記のようなセルライブラリのトラック数削減を続けざるを得ないが、EUVを用いることができれば、3nmデバイス設計でも、5トラックに留まる可能性があり、FinFETの延命を図れるとSteegen氏は指摘したが、その詳細についての説明を行わなかった。

FinFETはいつまで使えるか?

それでは、FinFETはこの先、どの程度まで微細化が可能なのだろうか。

FinFET(14nm、7nm、5nm、および3nmプロセス)および3nmナノワイヤの電力性能(消費電力vs動作周波数)を示したものが図3だ。これまでのimecの研究成果から、FinFETは5nmプロセスまで適用可能とされているが、もしEUVリソグラフィが実用化されれば、3nmプロセスまで適用することができるという(とはいえ、先般、[IBMは5nmプロセスにおいて、FinFETではなく、動作可能な積層シリコンナノシートFETを公開するなど、次世代に向けた動きが活発化してきている)。

Steegen氏は、「3nmプロセスでは、FinFETとナノワイヤでは、ほぼ同じ性能を実現する場合においては、専有面積を考えなければFinFETがベストソリューションだが、専有面積と性能のトレードオフを考慮するとナノワイヤに軍配が上がる。ナノワイヤは、ゲートピッチのさらなる微細化が可能だからである」と語っている。

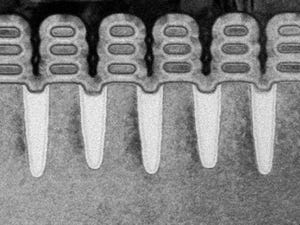

図4はナノワイヤFET(PチャンネルFETおよびNチャンネルFETで構成されたCMOSアーキテクチャ)の断面SEM写真だが、このデバイスの高性能化に関しては、ナノワイヤを多段積層して駆動電流量を増やしたり、チャンネルにキャリア移動度が従来のSiより大きなGeやIII-V属化合物半導体を用いることで、高速動作を可能にする試みが行われている。

3nm以降はシステム技術とプロセス技術の同時最適化で実現

3nm以降の微細なノードでは、これまで以上にシステムエンジニアやプロセスエンジニアが密接に協力しあって、システムと技術の同時最適化を図らなければ、高性能は実現できない(図5右上の楕円上の表記参照)。このことは、すでに2016年のITFでimecのLuc Van den hove社長が研究の基本方針として言及していた。

もはや一種類のトランジスタだけを用いるのではなく、システムの要請に応じてシステムLSI(SoC:System-on-Chip)の機能ブロックごとにさまざまな新規デバイスを適材適所で活用するということである。これについては、次回、具体的にどのようなことかを説明することとにしたい。

(次回は7月6日に掲載します)