Steegen氏が掲げたimecの高性能ロジックICのトランジスタ微細化ロードマップを以下の図1に示す。図の上だけの話とはいえ、ロードマップに3nmを0.7倍した(面積では0.7×0.7≒0.5倍した)2nm、それをさらに0.7倍した1.4nm(14オングストローム)まで記載されているのには会場からどよめきが起きた。

同氏は、いままでも微細化については楽観的で、幾多の困難を乗り越えて、IBMと競って世界の先頭を走ってきた経緯を説明し、これからもトップランナーとして闘志を漲らせて走り抜ける意欲を示す。ちなみに同氏は、imecがIBMの半導体研究チームから引き抜いた逸材で、IBMの内情を知り尽くした人物でもある。彼女は、もともとベルギー出身でimecの設立母体である地元KUL(ルーベン・カトリック大学)の出身であり、いわば米国へは武者修行に出ていたということとなる。

回路設計とプロセス技術を同時に最適化

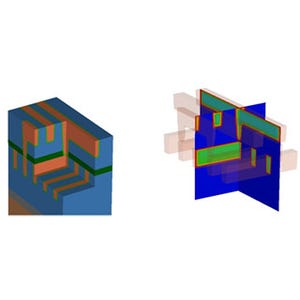

高速ロジックICにより多くのトランジスタを搭載してトランジスタ1個当たりのコストを最小化する、言い換えれば、ムーアの法則を延命させるためには、回路設計とプロセス技術を同時に最適化しなければならないこと(以下の図の中央の楕円の表現)は、2016年のITFにてimecのVan den Hove社長が研究の基本方針であると述べていた。

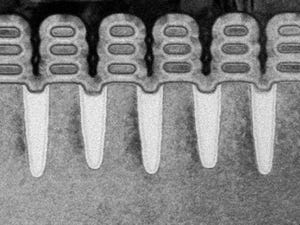

図にも示されているが、20nmノードからは、2重露光(ダブルパターニング)を採用せざるを得なくなったため、リソグラフィ-エッチングの繰り返し(いわゆるLELE)工程が加わり製造コストが上昇した。14~10nmではマルチパターニングを採用せざるを得なくなり、コストはさらにつり上がることとなる。imecのパートナー企業では7nmからEUVを生産に採用することでシングルパターニングに戻し、コストを下げる予定である。また、微細化が3nmを切るあたりからはEUVリソグラフィのN.A.(開口率)を上げてEUVの延命を図る予定だという。

EUVはレジスト、マスク、光源に注目

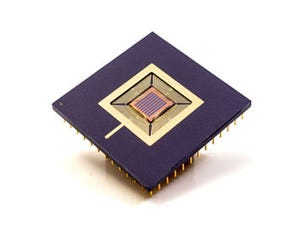

imecは従来から蘭ASMLとEUVリソグラフィの実用化で排他的(ライバルのニコンやキヤノンとはこの分野に関しては協業しない)な協業体制にある。ASMLはハードウェアの研究開発および製造は、オランダのアイントホーフェンにある本社で行っているが、リソグラフィのプロセス開発は、ベルギーのルーベンにあるimec本社の300/450mmクリーンルームに設置された最新のEUV露光装置で行っている。

Steegen氏は、「EUVリソグラフィは2020年初頭までには7nmプロセスによる実用化が見込まれている」との見解を以前から示しているが、そのめどが立ったという。現在、imecでは、最後まで残っている最重要課題である(1)EUVレジスト、(2)レチクル、(3)光源の3点にまつわる問題を重点的に検討している。

まず、レジスト関連の検討だが、当面の目標にしている露光量が20mJ/cm2に近づくにつれてライン・エッジのラフネス(粗さ)が増大してしまうという課題の解決を目指している。この課題解決のため、東京エレクトロン、ASML/米Lam Research、蘭ASMなどと個別にレジストプロセスやエッチングの最適化してエッジラフネスの軽減を研究しており「いわゆるスムージングの研究は今後も進めていけると確信している」と話す。

また、EUVリソグラフィでは、微小パーティクル(異物微粒子)が露光用マスクに付着して製造歩留まりを低下させる問題が顕在化しているが、imecでは、露光用マスクをパーティクルから保護するペリクル膜の開発も進めている。カーボンナノチューブを使用することで、金属材料より100倍強靭で、EUV光を97%透過し、出力250WのEUV露光(周辺温度500℃超)にも耐え得るペリクル膜をすでに開発済みだという。

なお、EUVの光源開発自体は、imecの管轄ではなく、ASMLの担当なのだが、リソグラフィのスループットに関しては共同で向上に努めている。スループットは、2014年初頭のころは10枚/時しか出せなかったが、2017年2月には100枚/時を超えたとのことで、Steegen氏は、ASMLとimecとの協業体制により、EUVリソグラフィの実用化は7nmの量産に適用可能な方向で着実に進捗していることを強調した。

(次回は6月29日に掲載します)