IEDM 2022で発表される200件余りの一般講演の中から、同プログラム委員会が選んだ注目論文5件を今回と次回の2回に分けて紹介したい。

世界初となる2Dゲートオールアラウンド(GAA)デバイスのデモ(TSMCほか)

Paper #34.5, “First Demonstration of GAA Monolayer-MoS2 Nanosheet nFET with 410 μA/μm ID at 1V VD at 40nm Gate Length,” Y-Y. Chung et al, TSMC/National Yang Ming Chiao Tung University/National Applied Research Laboratories Taiwan

ゲートオールアラウンド(GAA)構造のシリコンナノシートトランジスタは、次世代デバイスアーキテクチャとして最も有望な候補と見なされている。

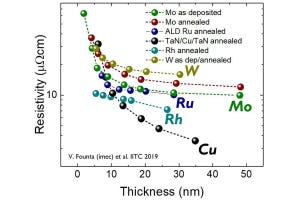

現在、ゲート長のスケーリング(比例縮小)と高度な静電制御は、ソース-ドレイン間のSiチャネルを薄くすることによって実現されているが、将来的には、単層TMD(Transition Metal Chalcogenide:遷移金属ダイカルコゲナイド)を使用することで極端なゲート長スケーリングの可能性がある。チャネル材料として単層TMDと統合されたシリコンナノシートは有望であるが、そのようなデバイスの性能とその潜在的な製造プロセスの両方を研究する必要がある。

TSMCと台湾の国立大学・国立研究所のチームは、2D単層TMDチャネルデバイスの集積フローを開発し、スタックされた2Dシートアーキテクチャにおける重要な課題を明らかにした。TSMCらはこれらの洞察を利用して、史上初の単層MoS2ナノシートFETをGAA構成で試作した。ゲート長は40nm、単層チャネルの厚さは約0.7nmである。トランジスタはVDS=1VでIONは約410μA/μmを達成した。FETのION/IOFF比は1E8を超え、正のVTHは約1.4Vで、DIBL(Drain-induced barrier lowering:ドレイン誘起障壁低下)はほぼゼロだったという。TSMCの研究者らは、複数のチャネル層を積み重ねることで、より高い駆動電流を実現できると主張している。

-

図1:単層MoS2ナノシートデバイスの断面TEM写真。ゲートがチャネルを完全に囲んでいる(左)、右は対応するEDX元素マッピング(サンプル内の元素の空間分布を示すために使用される手法) (出所:IEDM、以下すべて)

最も小型かつエネルギー効率の高いMRAM(Samsung Electronics)

(Paper #10.7, “World-Most Energy-Efficient MRAM Technology for Non-Volatile RAM Applications,” T.Y. Lee et al, Samsung

現在、nvRAMはニッチ市場にのみ対応しているが、新興市場向けの低リークワーキングメモリソリューション(キャッシュメモリなど)としての関心が高まっている。

IoTのスマート化(AIoT)やエッジAIコンピューティングアプリケーションなど、大量のデータ収集と分析に依存するアプリケーションなどが想定されており、これらのアプリケーションでは、総消費電力を下げることが重要となっている。

今回、Samsungの研究者たちは、これまでに報告されてきたMRAMと比べて、より小型かつエネルギー効率の高いスタンドアロンnvRAMメモリについて報告する。

28nm組み込みMRAMテクノロジに基づいて製造され、書き込みエネルギーは25pJ/ビット、54MB/秒で14mW(読み取り)/27mW(書き込み)の有効電力要件を実証したとする。また、従来と比べると小型のパッケージ寸法(16Mビットで30mm2)と、本質的に無制限の耐久性(>1E14サイクル)も備えているという。

デバイスのアーキテクチャの重要な部分は、磁気トンネル接合(MTJ)である。MTJを14nm FinFETプロセスに縮小した結果、面積スケーリングが33%向上し、読み取り時間が2.6倍高速になったという。これは、このテクノロジーが低リークのワーキングメモリとして機能する可能性を示しているとSamsungの研究者たちは主張している。

(次回は11月18日に掲載します)