Hot Chips 31においてNVIDIAは、研究中のマルチチップのAIチップを発表した。AIなどのチップの規模は増大しており、1チップにするには大きすぎる。AIチップではないが、AMDはCPUチップを細分化し、I/Oチップと合わせてインタポーザに載せるというやり方を採っている。こうすれば個々のCPUチップは小さいので歩留まりが高く、低コストで作れるという。

AI用のエンジンでも事情は同じで、大きなチップを複数の小さなチップに分けて、インタポーザに載せて相互接続して、大きなチップと同じ、あるいはよりメリットが出せれば都合が良い。このような可能性を探るのが、今回発表されたNVIDIAの研究チップである。

発表を行ったのはNVIDIのSenior Research ScientistのRangharajan Venkatesan氏である。

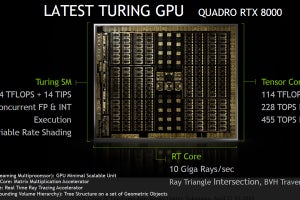

NVIDIAの研究部門はグラフィックス、ディープラーニング、ロボティックスなどの研究を行っており、Turing GPUに搭載されたレイトレース機能「RTX」、Volta GPUを高速で接続するNVLinkのスイッチである「NVSwitch」、GPU用のニューラルネットワークライブラリ「CuDNN」などは研究部門の最近の成果であるという。

実は、NVIDIAは研究用のテストチップをRC12、RC13、RC16、RC17と作り続けており、今回発表するものは「RC18」であるという。

なお、枠の外にさりげなく書かれているが、NVIDIAの研究者の数は200人と書かれている。筆者の感想を言うと、売り上げから言って、もう少し研究者が多くても良い感じがする。

-

NVIDIAの研究部門の概説。200人の研究者でグラフィックスやディープラーニングの研究を行っている。テストチップは、ずっと開発してきており、今回発表するのはRC18である (出典:この連載のNVIDIAの研究チップの部分のすべての図は、Hot Chips 31でのRangharajan Venkatesan氏の発表スライドのコピーである)

このテストチップを作る目的は、ディープラーニングの推論エンジンのスケーラブルなアーキテクチャを確立することである。そして世界でトップクラスの性能/Wを実現することである。

また、生産性の高い設計メソドロジを確立することも重要な目的である。

このテストチップでは47.5mm角のパッケージに36個のチップを取り付ける。各チップは2.5mm×2.4mmで、重み分散型の推論処理を行なう。

このようなマルチチップ型にすると、シリコンチップの製造に使われるレティクルのサイズより大きいシステムが作れる。また、小さなシリコンチップは歩留まりが高いし、設計費用も安くなる。そして、異なる半導体テクノロジを使うチップを混載することができる。

一方、チップ間の通信のレーテンシやバンド幅、チップ間接続に必要なチップ面積や消費電力のオーバヘッドが問題とならないかが気になる。

-

47.5mm角のパッケージに6×6=36個のチップを搭載する。チップは2.5mm×2.4mm。この方式ではレティクルより大きいシステムが作れる。そして、小さいチップは歩留まりが高く、設計も簡単。問題は、チップ間の通信のレーテンシとバンド幅。また、通信のインタフェースの面積、電力オーバヘッドも問題

チップ間の通信には、階層的な通信アーキテクチャを使った。チップ内の接続は4×5のメッシュ、チップ間の接続には6×6のメッシュを使った。

チップ内のメッシュで16個のPEと1個のグローバルPE、1個のRISC-Vチップを接続している。このネットワークはカットスルールーティングを行い、ブロードキャストもできる。ホップ当たりの遅延は10nsで、リンク1本で~70Gbpsのバンド幅を持っている。

パッケージ上のネットワークは6×6のメッシュで36チップを接続する。各チップはパッケージ上のネットワークのルータを持っている。そのルータはメッシュを構成する4本のチップ間接続インタフェースを持っている。ホップあたりの遅延は~20nsで、通信バンド幅はリンク当たり最大100Gbpsである。

-

オンチップのネットワークは4×5のメッシュ。16個のPEとグローバルPE、RISC-Vチップを接続する。遅延は1ホップ10ns。~70Gbpsのバンド幅。パッケージのネットワークは6×6。1ホップの遅延は~20ns。バンド幅は最大100Gbps

チップ間の信号伝送はGround-Referenced Signaling(GRS)という方式を使っている。この方式はグランドを中心とした振幅200mVの信号を送る。振幅が小さいので1.6pJ/bitと消費エネルギーが少ないという特徴がある。また、データは4本をシングルエンドとし、それに1本の差動のクロックを付ける。この構成は4bitのデータを6本の信号線で送ることができ、個々の信号を差動にして2本の配線を使うよりも配線の本数が減り、ドライバ/レシーバの面積を減らせるだけでなく、消費エネルギーも減らせる。

-

チップ間の信号伝送はグランドを中心に200mVの信号でシングルエンド伝送するGround-Referenced Signalingを使う。伝送速度はピン当たり25Gbps。消費エネルギーは1.6pJ/bit

(次回は9月30日に掲載します)