Hot Chips 27においてOracleは、「Sonoma」と呼ぶ新しいプロセサを発表した。

|

|

|

Sonomaを発表し、Q&Aに対応するOracleのBasant Vinaik氏(右)とRahoul Puri氏(左) |

2014年のHot ChipsでOracleが発表したハイエンドサーバ向けの「M7プロセサ」では、DIMMの接続には専用のインタフェースチップを使い、InfiniBand(IB)はPCIeを出すI/O Hubチップを経由し、さらにIB NIC(Network Interface Card)を必要とする。これに対してSonomaはDIMMやIBケーブルをCPUに直結でき、コンパクト、低コストにスケールアウト型のサーバを作れるというのがうたい文句である。

SonomaではInfiniBandのHCAを内蔵

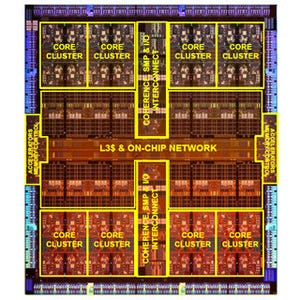

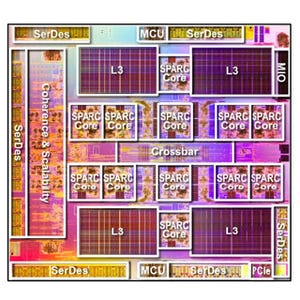

SonomaはM7プロセサと同じ第4世代のS4 SPARCコアを、8個搭載するチップである。セキュリティやデータベースの加速機構をハードウェアに組み込んでいるのもM7と同じである。Sonomaで新しいのは、DDR4メモリの直付けとIB HCA(Host Channel Adapter)を内蔵しているという点である。

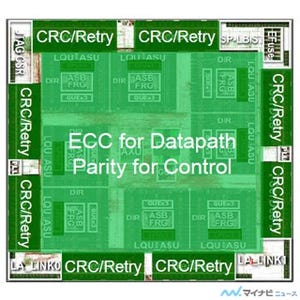

製造プロセスは20nmで、13層配線となっているが、チップサイズやクロック、消費電力などは発表されていない。これまでの例から見て、2016年2月のISSCCで発表されるのであろう。

次の図にブロックダイヤを示した2イシューのOut-of-Order(O-o-O)実行で、最大8スレッドを並列実行するS4コアは、2014年のHot Chipsで発表されたM7プロセサと同じコアである。

また、2コアで256KBのL2データデータキャッシュを共用し、これを2つ(合計4コア)で256KBのL2命令キャッシュを共用し、8MBのL3キャッシュのローカルパーティションが付くというコアクラスタの構造もM7と同じ作りである。

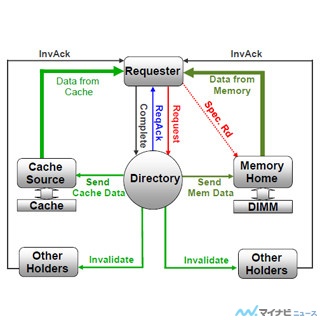

Sonomaの新機軸の1つがDDR4 DIMMを直結できるようにMemory Interfaceを内蔵した点である。大規模サーバ向けのM7では接続できるDIMMチャネル数を増やすために専用のDIMMインタフェースチップを外付けしていたが、M7ほどのメモリバンド幅、メモリ容量を必要としないSonomaではDIMMは4チャネルとして、インタフェースを内蔵した。

これにより、構成が簡単になり、余分なチップを経由しない分、アクセスレーテンシも短縮されている。とは言っても、他社のプロセサではDIMMを直結する方が普通であり、特に新奇な技術ではない。

また、DDRメモリからL3キャッシュに投機的に読み込んでメモリレーテンシを短縮する機能を実装している点はM7と同じである。

IntelのXeonサーバでも一番の売れ筋は、2ソケットのサーバで、これをEthernetなどで繋いでクラスタにするという使い方が多い。Sonomaは、このようなクラスタのシステムを狙ったプロセサであるが、Ethernetではなく、より高性能のInfiniBandを使うところが異なる。しかも、普通はIB HCAカードをPCIe経由で接続するが、SonomaではCPUチップに2リンク分のFDR IB HCAを集積しており、IBリンクをプロセサに直結できるようになっている。筆者の知る限り、IB HCAを内蔵するプロセサチップは初めてである。

IB HCAのIPはMellanoxから購入したのかと思ったのであるが、Oracle関係者の話によると、社内開発であるとのことであった。

また、Sonomaは、IntelのQPIに相当するCoherence Linkと呼ぶプロセサ間を繋ぐリンクを4本持っており、複数ソケットの構成も実現できる。各リンクのバンド幅は両方向合わせて128GB/sとなっている。しかし、図にはCL ×8とも書かれており、M7と同じで64GB/sのリンクが8本存在する可能性もある。

ロジックの動作から消費電力を計算してクロックと電源電圧を制御

Sonomaは各コアとL3キャッシュの動作をモニタして、動作に基づいてダイナミックな消費電力を算出するPower Estimatorを持っており、250ns間隔で消費電力を計算する。そして、その情報はPMC(Power Management Controller)に送られ、PMCはすべてのEstimatorからの情報やセンサからの温度や電流の情報を総合し、ソフトウェアから指示された電力管理ポリシーに基づいて電源電圧やクロック周波数を制御する。Power Estimatorが計算する電力値と実測との誤差は数%と書かれており、非常に精度の高い電力値がリアルタイムに得られる。このような制御はIntelやAMDのプロセサでも使われており、プロセサの電力制御の標準的な手法になってきている。

|

|

|

Sonomaでは各コアとL3キャッシュのアクティビティから消費電力を計算するPower Estimatorを持ち、PMC(Power Management Controller)が情報を総合して電源電圧やクロック周波数を制御する |

(次回は9月10日に掲載します)