Ravenでは電源変動は大きいが変換効率の高い方法を採用

普通、スイッチドキャパシタDC-DCコンバータでは、例えば4個のユニットセルを使う場合は、ユニットセルの接続を時間をずらせて切り替えることにより、電圧変動を小さくするのが一般的である。しかし、この方法では、1番目のユニットセルが放電し、2番目のユニットセルを並列に接続する時に、2番目のユニットセルの電荷はチップに供給されるだけでなく、1番目のユニットセルを充電することにも使われる。この電荷の再配分である程度のエネルギーが消費されるため、変換効率が下がってしまう。

このため、Ravenでは、すべてのキャパシタを同時に切り替える方式を採用した。電源電圧の変動幅は大きくなるが、変換ロスは小さく抑えられる。なお、Ravenでは電源電圧に追従してクロック周波数を可変することにより、大きな電源電圧の変動を許容する設計になっている。

この適応型のクロックは、クリティカルパスを模したレプリカ回路を作り、その回路の遅延時間が大きければクロック周波数を下げ、遅延時間が小さければクロック周波数をあげるという方法で電源電圧が大きく変動しても動作するようになっている。

Ravenでは、1.8Vの供給電源から1/2の~0.9Vを作り、1Vの供給電源から2/3の~0.67V、1/2の~0.5V電圧を作り出し、元の1Vと合わせて、合計4つの異なる電圧をチップのそれぞれの電源ドメインに供給することができる。スイッチドキャパシタでは、連続的に電源電圧を可変することはできないが、DVFSに使用するという観点からは、このように、適当な刻みの電圧が作れれば十分である。

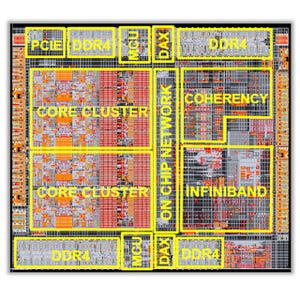

Raven3チップのアーキテクチャ

次の図は今回発表のRaven3チップ全体のアーキテクチャを示すもので、左側がスイッチドキャパシタのDC-DCコンバータ回路で、右側にRISC-Vのスカラコアとベクトルアクセラレータ、そしてキャッシュを含むコア部が描かれている。

このチップは28nmプロセスで作られ、コア部の面積は1.19mm2であるという。

このスカラコアは「Rocket」と呼ばれ、64bitアーキテクチャの5段のパイプライン構成のインオーダ実行コアである。なお、普通の整数の演算は1サイクルであるが、浮動小数点演算は3サイクルを必要とする。

64エントリのBTB(Branch Target Buffer)、256エントリのBHT(Branch History Table)、2エントリのRAS(Return Address Stack)を持ち、投機実行は行わないが分岐命令の処理を高速化している。また、MMUを持ち仮想メモリをサポートしている。

次の表はARM Cortex-A5とRISC-V Rocketコアを比較したもので、Rocketコアは、DMIPS/MHz性能はARMより10%高く、キャッシュを除くコア面積は半分、キャッシュを含めても73%程度と小さい。また、コア面積が半分であるので、ダイナミック消費電力も半分程度である。

このRocketコアに「Hwacha」というプロジェクトで開発したベクトルユニットを付けている。Hwachaは8要素のベクトルをSystolic Array的に処理する構造になっている。なお、Hwachaは整数演算器はバンクごとに持っており、1サイクルに8演算を実行できるが、チップ面積を減らすため、64bit整数の積演算器や浮動小数点の積和演算器は図の右端に書かれた1個のユニットを8個のバンクで使い廻している。このため、1サイクルに1演算しか実行できないという構成になっている。

|

|

|

Hwachaベクトルユニット。8個の整数演算器を持ち8要素のベクトルを処理するアーキテクチャであるが、面積の大きい64ビット乗算器や浮動小数点演算器は1個しか持っておらず、これでベクトル要素を順に処理する |

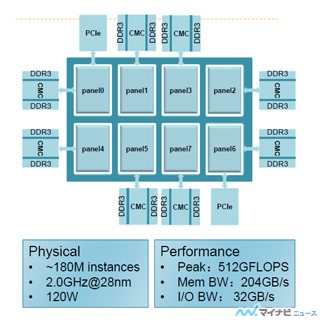

次の図はチップ写真で、STMicroelectronicsの28nmのFDSOIプロセスで作られ、チップサイズは1.3mm×1.8mmとなっている。この中で、スイッチドキャパシタの電源回路の面積は0.19mm2で16%の面積オーバヘッドとなっている。

(次回は9月20日に掲載します)