Bixbyチップの概要

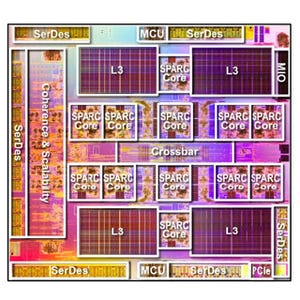

Bixbyチップは、次の図のように、24の入力ポートと24の出力ポートを持ち、24×24のクロスバを構成している。そして、この図に見られるように、左側にデータの通路を切り替えるクロスバがあり、右側にディレクトリを管理するブロックがある。ディレクトリは8つのASU(Address Serialization Unit)からなり、8つのディレクトリアクセスを並列して処理することが出来るようになっているのであるが、ディレクトリアクセスには2サイクルかかるので、1サイクルには4アクセスの処理となっている。

BixbyチップはM6プロセサと同じ28nmプロセスで作られ、96個のトランシーバと約20MBのディレクトリ用のSRAMと、クロスバやASUのロジックなどを集積している。0.85Vという低めの電源電圧で動かしているとのことであり、クロックはそれほど速くはないと考えられる。

96ソケットのシステムでは、96個のM6プロセサチップを24個のBixbyチップで接続している。つまり、48MB×96個のL3キャッシュラインの状態を20MB×24個のディレクトリでカバーしていることになる。L3キャッシュのラインサイズは64Bであるので、1個のBixbyチップで3Mラインの状態を管理しており、1ラインあたり6バイトあまりのメモリを持っていることになる。この程度あれば、アドレスの上位ビットのタグと、データの輸出先の8チップグループをビットマップで記憶できると思われる。

また、次の図に示すように、6個のBixbyチップのグループの中で1個のチップが故障してもシステムをブートすることができ、修理を行わなくてもシステムを使えると言う点で、可用性(Availability)高めている。なお、動作中にBixbyチップが故障すると、ディレクトリがなくなってしまうので動作は続けられず、システムをリブートすると、故障したBixbyチップを外してネットワークを構成するということになると思われる。

各所に誤動作/システムダウンの防止に向けたECCやCRCを搭載

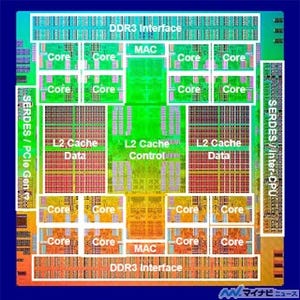

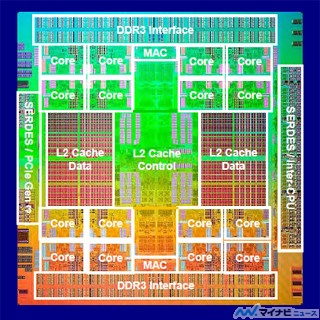

大型サーバは誤動作やダウンした場合の影響が大きいので、SPARC M6プロセサでは、アーキテクチャレジスタ、キャッシュ、内部のデータバスなどはECCをつけてエラー訂正を行っている。また、C-Link、S-Link、BoBチップへのリンクなどはCRCでエラーを検出して再送で訂正を行っている。

SPARC M6では、プロセサ1チップに最大1TBのメモリが付く。このため、メモリのエラーの頻度はPCなどに比べて高くなる。一方、大規模サーバは企業や社会インフラとして使用されるので、エラーの影響が大きい。

このため、メモリに対しては2重3重のエラー防止や回復手段が用意されている。まず、DRAMのECCは普通であるが、ECCの付け方を、DRAM素子の故障モードに合わせて最適化している。そして、ECCでエラーが検出された場合は、エラーを訂正したデータをDRAMに書き戻している。また、スクラバーで定期的に全アドレスを循環して読み出してエラーを調べ、訂正可能なエラーなら訂正してDRAMに再書き込みを行っている。このように出来るだけ早い時点で訂正可能なエラーを修正して、エラーが累積してECCで訂正できなくなるリスクを小さくしている。

また、E-retryという手法で、エラーを訂正したビットをチェックし、一過性のエラーか、DRAMそのものの固定故障かを判別するという。そして、固定故障が見つかると、Solaris OSは、そのアドレスを含むページを使わないようにする。また、特定のデータビットの配線やピンが故障した場合は、そのビットをスペアのビットで代替して運用を続けられるようになっている。

このようにSPARC M6は、最大96チップで9216スレッドを実行できる、業界でも最大規模のサーバである。そして、インメモリデータベースを効率よく動かすことを設計目標の1つとしており、最大96TBものメインメモリを持つ、キャシュコヒーレントな共通メモリシステムとなっている。また、大規模システムは企業や社会インフラとして使われるため、エラー訂正などのRASにも配慮したシステムとなっている。

なお、ブリッジチップのBixbyであるが、カリフォルニア州の太平洋岸を走る州道1号線にある景観の良い有名な橋の名前から付けられている。

|

|

|

本物のBixbyブリッジ ((C) Douglas Croft/2013 National Geographic Traveler Photo Contest) |