28nmプロセスで作られたメインストリームプロセサ「Kabini」

Hot Chips 25において、AMDは低電力APUのKabiniを発表した。Kabiniは4個のJaguarコアと、GCN(Graphic Core Next)GPUを搭載したAPUで、GCN GPUを搭載する初めてのAPUである。

Kabiniチップは28nmプロセスで作られ、チップサイズは105平方mm、トランジスタ数は914Mと発表された。100平方mm程度というのはメインストリームのプロセサとして、妥当なチップサイズである。

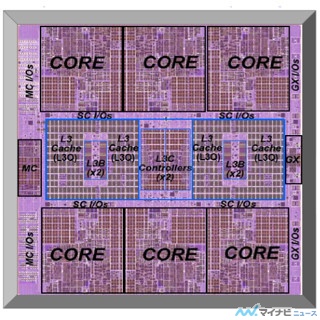

そして、Kabiniは4個のJaguarコアと2MBの共通キャッシュを搭載する。フロアプランを見ると、グラフィックスやマルチメディアエンジンがCPUと同程度か、多少広い感じの面積を占めており、AMDはグラフィックス性能が高いことをIntelに対する差別化要因として打ち出している。

KabiniのプロセサコアであるJaguarは、Bobcatにはじまる野生猫シリーズの第2世代のコアである。

BobcatからJaguarへの改良点

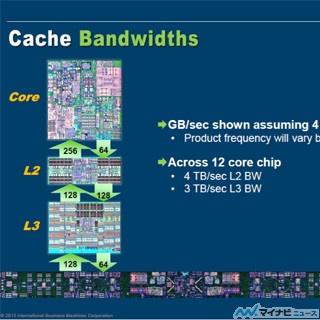

BobcatからJaguarへの改良点であるが、命令の供給に関しては、命令キャッシュからのプリフェッチの改良、命令バッファのサイズ拡大が行われており、実行ユニットでは、Out-of-Order実行用のリソースを追加したり、新設計の割り算器の搭載、CRC32/SSE4.2などの命令サポートを追加している。浮動小数点(FP)ユニット側では、演算器を128ビット幅に拡張し、単精度の場合は、毎サイクル4乗算と4加算を実行できるようになった。なお、倍精度の場合は、1乗算と2加算を実行できる。

そして、Intelの新SIMD命令である256ビットの演算を行うAVXをサポートしている。ただし、ハードウェアは128ビット幅であるので、256ビットの演算には2サイクルを必要とすると考えられる。

ロードストアユニットは、キューを再設計して効率を改善し、ページテーブルをたどる部分も効率を改善している。また、FPユニットの128ビット化に合わせて、FPユニットへのデータバスを128ビット化して、1サイクルでデータ転送ができるようになった。また、バスユニットでは、複数のWriteを1つにまとめる部分の改善、メモリアクセスの並列性を高める資源などの追加を行っている。

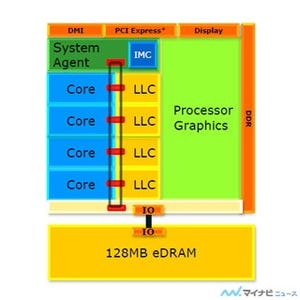

Kabiniでは4個のJaguarコアで2MBのL2キャッシュを共用する。L2キャッシュは4バンクに分割されており、バンクが競合しなければ4つのアクセスを並列に処理できるようになっている。

RADEON 8000 Graphic Core Next(GCN)アーキテクチャは、ディスクリートGPUでは、すでに製品化されているが、CPUと一緒に集積するAPUでは、Kabiniが最初の製品となる。GCNでは、従来のVLIW命令をやめ、単一命令のSIMT実行として、命令の実行密度を高めている。

そして、Kabiniでは、GCNのコンピュートユニットを2個搭載し、128KBのL2キャッシュを持たせている。

GCNのコンピュートユニットは、次の図に示すように、SIMD-16のベクタユニットを4個もっている。SIMD-16ベクタユニットは、毎サイクル16個の単精度浮動小数点の積和演算を実行することができる。従って、2個のコンピュートユニットを持つKabiniは毎サイクル128積和演算を実行する能力を持っている。

また、コンピュートユニットには、4個のテクスチャサンプラー、1個のスカラユニットと64KBのローカルメモリ(Local Data Share)が含まれている。

APUで難しいのは、GPUからメモリへの高バンド幅のアクセスの実現と、GPUとCPUのメモリのキャッシュコヒーレンシの実現を両立させることである。これに対して、Kabiniでは、キャッシュコヒーレンシを維持した単一メモリ空間を提供するFCLというリンクと、GPUからコヒーレンシメカニズムをバイパスしてメモリをアクセスするRadeon Memory Busを設けるという方法で解決している。FCLは128ビット幅であるが、Radeon Memory Busは256ビット幅としてメモリアクセスのバンド幅を拡大し、更にキャッシュコヒーレンシ制御のオーバヘッドを除いて、高速データ転送を実現している。

Radeon Memory Bus経由のGPUからのメモリアクセスは、コヒーレンシが維持されないが、CPUからアクセスされることがないフレームバッファなどとして使う分には問題ない。また、CPUがアクセスする場合には、明示的の同期をとるなどの方法で矛盾を起こさないようにすることが出来る。

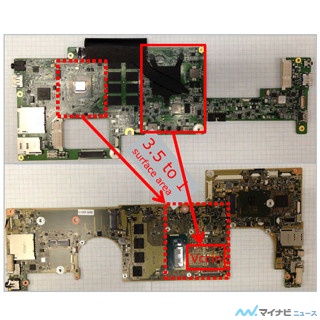

そして、Kabiniを使うシステムの全体像は次の図のようになる。メモリインタフェースはDDR3-1600を1チャネルで、最大2枚のSO DIMMを接続できる。そして、FCHからはPCI ExpressやUSB2.0、USB3.0、SATA3が出ており、ディスプレイコントロールからはeDP、HDMI、VGAなどが出ている。そして、LPC経由でキーボートなどが繋がり、SPI経由でBIOSを格納するFlashが接続される。