低コスト・高密度のDRAMへの需要はこれまでになく高まっているが、その一方でDRAMのPPAC(性能、消費電力、面積あたりコスト)の改善は物理的制約に妨げられている。

DRAMの容量は過去20年間にわたって順調に伸びてきたが、適切なソリューションがなければこの成長にブレーキがかかり、AIやハイパフォーマンスコンピューティングなどの分野の進歩も鈍化する恐れがある。

この課題に応えるため、Applied Materials(AMAT)はDRAMメーカー各社と協働してさらなる微細化と性能・消費電力を改善する新たな方法を創出するマテリアルズ・エンジニアリング・ソリューションに取り組んでいる。

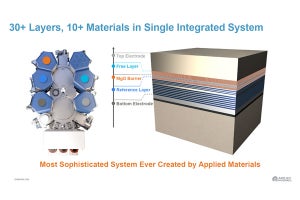

AMATは先般、DRAMスケーリングに向けた3つの鍵となるソリューションの発表を行った。1つはセルアレイキャパシタ形成用の新しいハードマスク材料、2つ目はインターコネクト配線用Low-k絶縁膜、そして3つ目はHigh-k/メタルゲート(HKMG)トランジスタをチップの周辺ロジックに採用することだ。

DRAMキャパシタのスケーリングを拡張する新しいハードマスク材料Draco

DRAMスケーリングの手法としてはキャパシタ径を縮小するのが一般的だが、十分なキャパシタ表面積を確保して電荷を維持するためにアスペクト比を高める必要がある。

それにはエッチングで深いキャパシタ孔を形成することが求められるが、ここで問題が生じる。キャパシタ孔のパターンを転写したハードマスク材料がステンシルマスクとして機能する限界を超えてエッチングされる恐れがあるのだ。細孔を高エネルギーイオンでエッチングする際、同時にハードマスクもエッチングされる。キャパシタ孔が完全に形成される前にハードマスクがエッチングされ消失してしまうと、キャパシタ孔のパターン形状が崩れる。一方、ハードマスクを厚くすると、アスペクト比がさらに高くなるうえに、キャパシタ孔にエッチングの副生成物が残留し、孔のねじれや曲がり、エッチング不足、その他のキラー欠陥を引き起こす。

この課題を解決するため、AMATは従来のハードマスクよりも固く高密度な新しいハードマスク材料を開発した。この「Dracoハードマスク」を使用するとエッチング選択性が30%以上高まるので、マスクの膜厚をより薄くすることができる(図1)。

DracoハードマスクはAMATのエッチング装置「Sym3 Y」と合わせて使えるよう協調して最適化されており、プロセスを電子ビーム測定・検査装置「PROVision」でモニターすることにより、毎時50万回近い計測を行うことができる。

この協調最適化は、高度なRFパルスによってエッチングと副生成物除去を交互に行って同期させ、まっすぐで均一な正円柱のパターン孔の形成を可能にする。これにより、DRAMスケーリングの最大の課題の1つであるキャパシタ形成のばらつきが低減する。さらに、Dracoハードマスクは副生成物が揮発性となるように作られているため、円柱形のキャパシタ孔内壁に副生成物がこびりつかず、厳しいエッチング条件下でも従来のハードマスクより容易に除去できる。

このほか電子ビーム検査装置PROVisionは、大量のデータを生成してキャパシタの均一性を左右するハードマスクのCD均一性に関して実行性ある洞察を提供する。AMATのソリューションは局所的なCDばらつきを50%改善し、ブリッジ欠陥を100分の1に低減してユーザー企業の歩留まり向上を実現する(図2)。

DRAMスケーリングの鍵となるあと2つは、周辺回路エリアの面積縮小に関連するものだ。これは、DRAMセルアレイを囲むエリアで、ロジックトランジスタと配線で構成される。ロジックトランジスタの性能を強化してリークを防止すると同時に、インターコネクト配線間の距離を縮めてDRAMを高密度化することである。AMATは、この両方についてのソリューション開発を支援している。

Low-k絶縁膜Black DiamondをDRAM市場に投入

金属配線は、どれも絶縁材料で覆われている。配線層を縮小化することでDRAMのダイサイズは縮小されたが、それが新たな技術課題を生んでいる。層間絶縁膜が薄くなりすぎて、金属線の容量性カップリングを防ぎきれなくなり、信号が相互干渉を起こして消費電力増、低速化、発熱増大、信頼性低下などのリスクを招いているのだ。

金属配線の絶縁材料には、これまで25年近くにわたってシランないしテトラエトキシシラン(TEOS)のいずれかのシリコン酸化物が用いられてきた。AMATはこれらのシリコン酸化膜が限界に達したという認識により、DRAMの導線をより近く配置しても信号の干渉を回避できるような低キャパシタンスの絶縁材料が必要である、と考えた。

そこで、Low-k絶縁材料「Black Diamond」をDRAMに活用する方法を探ることにした。Black Diamondは、AMATがかつて先端ロジックデバイスのスケーリング課題を解決するために開発した材料だ。

Black Diamondはドーパントにカーボンを用いており、より微細でコンパクトなインターコネクト配線を実現するので、信号がDRAM内を数GHzの速度で行き来しても、キャパシタンス、消費電力、クロストークを低く抑える。

ユーザー企業のプロセスフローへのシームレスなインテグレーションを実現するため、このLow-k材料は優れた界面制御性と成長層への吸着性を備えている。現在、将来世代のDRAMに向けた新しいBlack Diamondの開発をユーザー企業と共に進めている。

HKMGトランジスタでDRAMのPPACを改善

周辺ロジック回路に用いられるトランジスタはI/O(入出力)操作を駆動するもので、今日のDDR5規格DRAMに求められる性能の確保に重要な役目を果たす。

これまでDRAMにはポリシリコン酸化膜ベースのトランジスタが用いられてきたが、ファウンドリ・ロジック分野ではこの種のトランジスタは28nmノード以降あまり使われていない。なぜなら、ゲート絶縁膜がきわめて薄くなると電子リークが生じやすくなり、電力消費と性能に悪影響を及ぼすからだ。ロジックメーカーが代わりに採用したHigh-k/メタルゲート(HKMG)トランジスタは、ポリシリコンに代えてメタルゲートが用いられるほか、絶縁膜にはゲート容量、リーク、性能の改善をもたらす酸化ハフニウムを採用している。

PPACの継続的改善を進めるため、メモリメーカーは先進的なDRAM設計にHKMGトランジスタを導入しつつある。ロジックと同様DRAMでも、いずれポリシリコントランジスタに代わってHKMGが増えてくるだろう。AMATは成膜や薄膜処理技術でのリーダーシップを生かし、この技術転換を推進している。

AMATの「Endura Avenir RFPVD」は前後の工程を真空内で処理できることから、複雑なHKMGスタックの製造に適したソリューションとして提供されている。さらに、「Centura RP Epi」をはじめとするエピタキシャル成長装置や、トランジスタの特性を詳細にチューニングして性能を最適化する「RadOx RTP」、「Radiance RTP」および「DPN」などの薄膜処理装置も、HKMGトランジスタの製造に寄与している。

まとめ

チップ製造に新しいマテリアルを導入するのはたやすいことではない。既存のプロセスフローへの組み入れはもちろん、上流・下流の工程とも互換性がなければならない。成膜とエッチングのプロセス相互作用を協調して最適化し、これに独自の測定技術を組み合わせることで、AMATはR&D学習サイクルを加速し、より優れた結果をさらに迅速にユーザー企業に提供している。

DRAMスケーリングに向けたAMATのソリューションは、その幅広い製品ポートフォリオと、これらの技術を独自に組み合わせ、実現する能力から生まれている。このソリューションはAMATの戦略「PPACtプレイブック」を実施するもので、新しいアーキテクチャ、3D構造、新しいマテリアル、ヘテロジニアスデザインと先進的パッケージングによる新たな微細化技術を生み出し、ムーアの法則に沿った従来のスケーリングの停滞を打破する。この新しいPPACtプレイブックは、DRAMメーカー各社が製品ロードマップを前進させ、より低コストで高性能なメモリを提供して、グローバルで起きている記録的な需要増に応えていくのを支援する。

著者プロフィール

Sony VargheseApplied Materials(AMAT)

セミコンダクタプロダクトグループ メモリ戦略マーケティング部門ディレクター

メモリ分野において今後鍵となる技術転換の課題を特定する業務に従事。

AMAT入社以前はMicron Technologyの研究開発部門で、メモリ技術の開発を担当。

申請中のものも含め、20以の半導体プロセスとインテグレーションに関する米国特許を保有する。

インド国立工業大学 スラスカル校で材料工学の修士号、オクラホマ州立大学で機械・材料工学の博士号を取得。