コデザインのやり方を図16に示す。まず、アプリケーションのカーネルを抽出して、それぞれのカーネルの実行時間を実行時間推定ツールを使って求める。そのやり方であるが、まず、(1)システムパラメタを設定し、(2)システムパラメタの条件でアプリケーションをチューニングする。(3)ツールを使って実行時間を評価し、(4)ハードウェアのボトルネックを見つけたら、システムパラメタを変更して(2)へ戻るというループを繰り返す。

なお、通信時間は通信パターンに基づく解析的モデルを使って実行時間を評価した。

コデザインで決めるパラメタとしては、

- 基本的なアーキテクチャ(Feasibility studyで決定)

- メニーコア、Out-of-order、SIMDなど

- 命令アーキテクチャとSIMD命令

- 富士通はArmと一緒にSVE命令を作った

- チップの構成

- CMG(Core Memory Group)のコア数、チップに載せるCMG数、コアとCMGの接続法、L1キャッシュの容量、Way数、スループット、L2キャッシュの容量など、オンチップネットワークの構造、チップサイズ、ノードに含むチップ数 など

- キャッシュの構造

- Out of order(O3)リソース

- ターゲットアプリケーション向けの性能向上

- ノード間のインタコネクト

- SerDes、トポロジ(Tofuを使うか別のトポロジか)

基本構成はFeasibility Studyの結果に基づいて決定した。

- 決定すべきパラメタ

- #CMG、#core/CMG、Network on Chip

- MCMとインタポーザ(有機プリント板、シリコン、ガラス、……)

- チップサイズはコストに影響する (図の右上のグラフ)

- 性能はHPLのような簡単なカーネルの解析モデルで推定

構成案としては図18の下半分に描いたように、小さなプロセサチップとHybrid Memory Cube(Micronの3D積層メモリ、FX100で採用)、大きなプロセサチップとHMC、小さなプロセサチップとHBMをMCMに搭載、大きなプロセサチップとHBMなどの案を検討し、結果として、「大きなプロセサチップとHBM」に決定した。

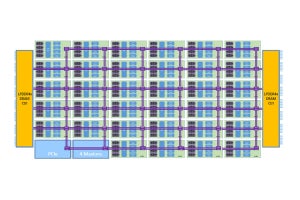

富岳のアーキテクチャチームは、いくつかのCMGとインタコネクトのインタフェースやI/Oを接続するPCIeインタフェースを搭載するチップを作ることに決定した。このチップのサイズはおおよそ400mm2で、7nm FinFETプロセスで製造するときのコストも、まあ、妥当な範囲に収まると考えられる。

最近のAMDのEpyc CPUのようにMCMを使う事も考えられたが、

- 小さなチップは歩留まりが良く、安く作れる

- しかし、パッケージングのコストが高い

- CPUとI/O、ネットワークで個別のチップを作る必要が出そうで、NRE(Non Recurring Engineering)費用が高くなりそう

- MCM上のチップ間配線が電力消費を増やしてしまう

図19の右下の表は、チップ上のコア数とMCMの枚数を変えてコストを試算したもので、ここでは全体で64コアを搭載するとしている。この表では、64コアを1チップに載せる場合のコストを1.0とすると、例えば16コアのチップを4個を1つのパッケージに搭載すると全体コストは1.03と多少高くなる。その他の案はさらにコストアップが大きい。

ただし、AMDと富士通ではコスト構造が異なる。AMDの方が生産量が多いので、開発のNREは相対的に安くなる。また、AMDのI/Oチップは12nmという古いプロセスを使っており、チップコストも安いと思われ、MCMも安いプリント基板を使っているので、この検討から、AMDのアプローチが間違っているとは言えない。

(次回に続く)