次の図の写真に写っている中央の部分がVEプロセサと6個のHBM2メモリからなるベクタエンジンで、これらのチップはシリコンインターポーザに搭載された2.5D実装となっている。VEプロセサはTSMCの16nm FinFETプロセスで作られ、チップサイズは15mm×33mmである。

なお、6個のHBM2メモリを搭載する製品は世界初であり、1.2TB/sというAurora TSUBASAの高メモリバンド幅を実現している。

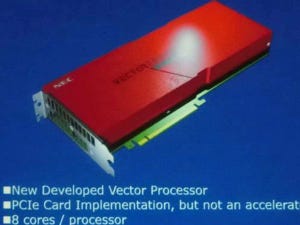

VEチップには8個のベクタコアが搭載されており、それに16MBの最終レベルキャッシュが付いている。

コアのクロックは1.6GHzで、コアは倍精度で307GFlopsの演算性能をもち、プロセサ全体では2.45TFlopsの演算性能となっている。6個のHBM2メモリのメモリバンド幅は1.2TB/sでメモリ容量は24/48GBである。

-

VEエンジンは8個のベクタコアと16MBのLLCとDMAエンジンを集積している。クロックは1.6GHzでコアのDP演算性能は307GFlops。6個のHBM2メモリを接続しており、メモリバンド幅は1.2TB/s

次の図がベクタコアのブロックダイアグラムである。左上がスカラユニット(SPU)で、高性能のスカラユニットを持っているので、アプリケーションをベクタコア側で実行することができる。ベクタユニット(VPU)は計算エンジンで、DPで307.2GFlops、SPで614.4GFlopsの演算性能を持つ。アドレス生成と変換部分はSPU、VPUのメモリアクセスのアドレス変換とメモリへの接続部分を含んでおり、ロード、ストアともに409.6GB/sのデータ転送ができる。

次の図はSPUのブロックダイアグラムである。SPUは4命令を並列に処理するOut-of-Orderの高性能プロセサであり、それぞれ32KBの命令、データキャッシュと256KBの共通2次キャッシュを備えている。SPUは高性能のプロセサとなっており、アプリケーションのスカラ部分の処理を担当しても比較的高い性能を持つと思われる。これが、Aurora TSUBASAでは、ベクタエンジン側にアプリケーションの実行を丸投げできる理由である。

一方、普通のGPUはアプリケーションの並列度の無い部分を高速に実行できるプロセサを持っていないので、アプリケーションを丸投げするという実行方法は採れない。

-

スカラユニットは4命令並列処理のOut-of-Order方式のプロセサである。そして、5本の実行パイプラインを持つ。32KBの1次命令キャッシュと32KBの1次データキャッシュ、256KBの命令、データ共用の2次キャッシュが付いている

次の図はベクタユニットのブロックダイアグラムである。実行パイプラインはFMA0、FMA1、ALU0/FMA2、ALU1/Storeの4本で、これが32組ある。従って、FMAを積と和の2演算と数えると、毎サイクル6演算×32回実行できる能力をもっている。

ベクタレジスタの総数は256個で、これらに64個のベクタアーキテクチャレジスタをマップしてOut-of-Order実行を行っている。

なお、ベクタ演算器は64bitの倍精度浮動小数点と2つの32bit単精度浮動小数点として扱うことができるが、ここの記述ではint16やint8に分割できるのかどうかは不明である。

メモリサブシステムは6個のHBM2メモリを8個のLLCスライスに対応させる構成になっている。HBM2メモリのバンド幅は1.22TB/s、LLCからベクタ演算パイプラインへのバンド幅は3TB/sである。そして、コア1個当たりのLLCバンド幅はread、writeともに409.6GB/sとなっている。

コアの演算性能はDPの場合で307GFlopsであるので、LLCのバンド幅は1.33B/Flops、HBM2のバンド幅は0.497B/Flopsとなる。これは他のスパコンよりも高いB/Flopであり、NECのベクタプロセサの面目躍如というところである。

-

6個のHBM2メモリを使い、1.22TB/sという高メモリバンド幅を誇る。LLCは16MBで、LLCとHBMのアドレス対応は固定のいわゆるMemory Side Cacheになっている。DMAエンジンやPCIeアクセスはリングバスでLLCをアクセスして読み書きを行う

NoCは2次元のメッシュネットワークになっており、前の図でNoCと書かれた灰色の箱の中身は次の図のようになっている。LLCからの16本のバスが横方向に描かれ、コアに繋がる16本のバスが縦方向に描かれており、それらの間が中央のオレンジの箱で描かれたクロスバで接続できるようになっている。

この部分は長い配線になるので、抵抗の低い上層の配線を使ってRC遅延を減らしている。さらに、パケットのヘダーの配線はスーパーエクスプレス配線、ペイロードはエクスプレス配線と細かく最適化した設計となっている。

そして、アダプティブなフローコントロールやエージベースのQoS制御を行っているという。

(次回は5月15日に掲載します)