高速読み出しでビデオ撮影が可能になった

光を受けてPDに発生した電荷はアンプで増幅され、セレクタトランジスタを通って縦方向の線を通して読み出される。読み出すピクセルを順次切り替えながら1つのA/Dコンバータ(ADC)でデータを読みとってデジタル化するのでは、全ピクセルを読み出すには長い時間がかかる。これを高速にするために、列ごとにADCを置く方式が使われている。この場合、高解像度のイメージセンサでは数千個のADCが必要となる。

また、さらに読み出しを高速にするため、各列に2個のADCを置き読み出し時間を半減する方式のものも出現している。

2006年に各列に1個のADCを置く方式イメージセンサができ、60フレーム/秒の読み出しが可能になり、ビデオの撮影ができるようになった。そして2014年には各列に2個のADCを置くイメージセンサが出現し、120フレーム/秒の読み出しができるようになり、フルHDのムービーが撮影できるようになった。

長短2回の露光でダイナミックレンジを拡大

晴れた日の直射日光のもとでの撮影などでは、コントラストが強すぎてイメージセンサのダイナミックレンジを越えてしまい画像が潰れてしまう。これに対して、長時間露光と短時間露光の撮影を行い暗い部分は長時間露光のイメージ、明るい部分は短時間露光のイメージを使う。あるいは両方の露光のデータを混合したイメージを使うことにより、ダイナミックレンジを広げ、白飛びや黒潰れのない画像を作るという技術が開発された。

露光タイミングを揃えて動くものも正しく撮影

各列にADCを持つイメージセンサでは、それぞれのタイミングでは横1列のピクセルのデータが読み出される。次の図の上側の図のように横1列ごとに順に処理をしていくと、列ごとに露光を開始するタイミングが少しずつずれて行く。タイミングがずれても、静止しているものは問題ないが、メロトノームの針のように動いているものはゆがんで写ってしまう。

すべてのピクセルの露光タイミングを一致させ、露光終了時点で、各ピクセルに設けたトランジスタ1個とキャパシタで構成されたメモリにPDの出力を記憶させ、その後、メモリを順次読み出すというグローバルシャッタ方式とすれば、このような歪みは発生しない。

|

|

|

通常の方式でピクセル列の位置で、露光されるタイミングが違ってくるので、動いているメトロノームの針が曲がってしまう。同時に露光してメモリに蓄積し、その後、順次にメモリから読み出すグローバルシャッター方式なら、このような問題は無い |

このような技術を使って、解像度では100Mピクセルというイメージセンサが作られ、感度ではISO 409600という明るさでもノイズが目立たないイメージセンサが作られている。フレームレートでは1000fps、ダイナミックレンジでは通常のイメージセンサは70dBであるが、これを130dBまで拡張している。

イメージセンサの性能を改善するには

イメージセンサの感度やダイナミックレンジを改善するには、素子に掛ける電圧を高める必要がある。一方、画像品質を悪化させるノイズは半導体結晶の欠陥に起因するものが大部分であり、ノイズ低減には、低温で長時間アニールをして欠陥を修復することが有効である。

ピクセル部とロジック部を3D積層しTSVで接続

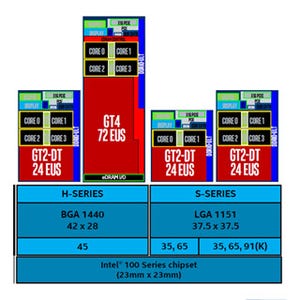

次の図に示すように、ピクセル部のトランジスタは高電圧動作、低ノイズが要求されるが、一方、ロジック部のトランジスタは低電圧動作、高速が要求される。ピクセル部は配線層の数は少なくて済むが、ロジック部は多くの配線層を必要とする。このようにピクセル部とロジック部で半導体プロセスに対する要件が大きく異なるので、次の図のConventional CIS(CMOS Image Sensor)の図のように、ピクセル部とロジック回路部を同じチップ上に作ろうとすると、それぞれに最適化した半導体プロセスは使えない。

この問題を解決するため、 2013年頃からは、ピクセル部とロジック回路部は別チップとして、それぞれの要件に最適化した半導体プロセスを使い、両方のチップをTSVで接続するStacked CISが主流になって来ている。

|

|

|

ピクセル部とロジック回路部ではトランジスタや配線層数など、半導体プロセスに対する要件が大きく異なる。このため、それぞれのチップを別個に作り、TSVで接続する3Dスタック方式のセンサが主流になって来ている |

3Dスタックは、次の図にみられるように、チップの縁の部分にTSVを設けてピクセルチップとロジックチップを接続し、ピクセル領域では単にピクセルチップの下にロジックチップがあるだけで、両者の接続はないという構造になっている。

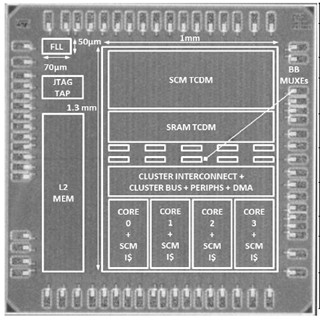

次の図はスタックされるピクセルチップとロジックチップの写真を示しており、ピクセルチップはメタル4層+ポリシリコン1層で、90nmプロセスで作られており、ロジックチップはメタル7層+ポリシリコン1層で、65nmプロセスで作られている。なお、ピクセルチップは1/1.7インチで20Mピクセルの裏面照射型で、ロジックチップはカラムごとに2個のADCを持つ先端のイメージセンサである。

次の図はロジック部のゲート数に対するチップサイズを示したもので、ピクセルチップのサイズが大きい場合はゲート数が増えてもチップサイズは変わらず、ピクセル部よりロジック部が大きくなるとゲート数の増加がチップサイズの増加に繋がる。したがって、ピクセル部とロジック部のサイズが同じになるところがスイートスポットであるという、当たり前の図である。

前の図をみるとピクセル部は90nmプロセスであるが、ロジック部は65nmプロセスを使っている。これはロジック部を90nmプロセスで作るとチップサイズが大きくなってしまいコストアップになる。一方、ロジック部により微細な45nmや28nmプロセスを使ってロジックチップを小さくしてもチップサイズはピクセルチップで決まってしまうので安くはならないということであろう。

|

|

|

ロジック部のゲート数が少なくチップサイズがピクセルチップで決まる範囲ではゲート数が増えてもチップサイズは変わらない。しかし、ゲート数が多くなりロジックチップの方が大きくなるとゲート数の増加がチップサイズに直接影響し、コストが上がってしまう。したがって、両方のチップが同じサイズになるあたりがスイートスポット |

次の図はソニーのCMOSイメージセンサの出荷量の年次推移を示したものである。イメージセンサの出荷量は急激に伸びているものの、使われているテクノロジを見ると2010年までは表面照射のCISであるが、感度の高い裏面照射型が出てくると、大部分が裏面照射型に取って代わられ、2012年にスタック型が登場すると、2013年には半分がスタック型、2014年には2/3がスタック型に置き換わるという進歩の激しい業界である。