電源電圧を下げた場合に問題となるのは、トランジスタの製造バラつきである。スレッショルド電圧(VT)の大きなトランジスタは、電源電圧がVTに近くなると電流が流れにくくなって回路が動作しなくなってしまう。一方、VTが小さなトランジスタは動作は問題ないが、オフ時のリーク電流が大きく、大きな電力を消費してしまい低電力化の障害となる。

そこでPULPが取り入れたのがUTBB FD-SOIという半導体製造技術である。次の図のように、ソース、ドレインを形成するシリコン層が非常に薄く、ゲートがその直下のチャネルを流れる電流をコントロールする力が強い。そして、チャネルの下に非常に薄い酸化膜層があり、次の図の左下の図のように、酸化膜層の下のシリコンに与える電圧(バックバイアス)でVTを可変することができる。

このBuried Gateと書かれている層に与える電圧が、順バイアス(FBB)の場合はVTは低下して電流が流れやすく(Ionの増大)なり、逆バイアス(RBB)の場合は電流が流れにくくなり、リーク電流を大幅に減らす(Ioffの減少)ことができる。なお、NチャネルトランジスタとPチャネルトランジスタでは与える電圧が逆になる。

トランジスタの特性バラつきは、量子力学的な原因で、個別にランダムにバラつくという要素もあるが、製造バラつきによるものは、ウェハ上の位置で緩やかに変化する。後者のバラつき成分は、領域ごとにトランジスタのバックバイアスを調整すれば、かなりの程度、特性のバラつきを抑えられる。

トランジスタに流れる電流が少なくトランジスタの動作速度が遅い領域には順バイアスを与え、トランジスタのリーク電流が大きい領域には逆バイアスを与えて調整することにより、低い電源電圧の場合の動作速度を引き上げ、リーク電流の大きな領域のトランジスタの電力消費を減らすことができる。

論理回路(ゲート)は、これで良いが、SRAMには問題が残っている。標準的に使われている6TrのSRAMセルはゲートほど低い電源電圧では動作しない。6Tr SRAMでは状態を記憶しているインバータのHighになっている出力を、ビット線に繋がっているパストランジスタで強引に引き下げて書き込みを行うというメカニズムを使っているためである。しかし、SRAMの電源電圧を下げられないと、消費電力を減らすことができない。

トランジスタを2個追加して、低電源電圧でも動作する回路にすれば電源電圧を減らすことはできるが、セルの面積が25%~50%増加する、動作時の消費エネルギーが増えるという問題がある。

ゲートと同じスタンダードセルを使ってメモリを作ると面積は2倍になってしまうのであるが、ゲートと同様に広い電源電圧範囲で動作する。また、読み書きに必要なエネルギーも1/2~1/4に減少する。

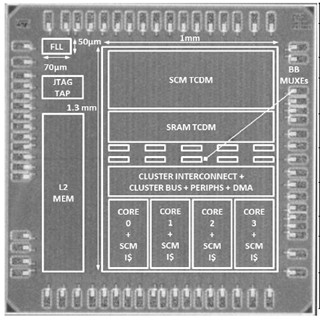

そこでPULPでは、L2キャッシュやI/Oインタフェースを含み、0.8V電源で動作させるSoC電圧ドメイン、プロセサコアや各種ロジックを含み、0.5~0.8Vで動作させるクラスタ電圧ドメイン、そしてSRAMを含むSRAM電圧ドメインの3種の電源領域に分けられている。なおSRAM電圧ドメインの電圧は0.5~0.8Vとクラスタ電圧ドメインと同じ範囲であるが、タイミング的に異なる電圧が必要となるので分離されていると考えられる。

なお、この基調講演の図では0.5Vからとなっているが、新しい論文では、最低電圧は0.32Vまで下がっている。