Gen9 GPUの構造

SkylakeのGPUのExecution Unit(EU)は7つのハードウェアスレッドを切り替えながら同時並行的に実行することができる。そして、スレッドアービタは7つのスレッドの命令の中から、2つのSIMD FPUで演算を行う命令、分岐命令、メモリのRead/WriteやI/Oなどを実行させるコマンドを送り出すSend Unitへの命令を選択して、それぞれのユニットに発行する。

SIMD FPUは32bit×4のMAC(Multiply-Accumelate)演算を実行するSIMD構造で、各EUは2つのSIMD FPUを持つので最大8個のMAC演算を実行できる。

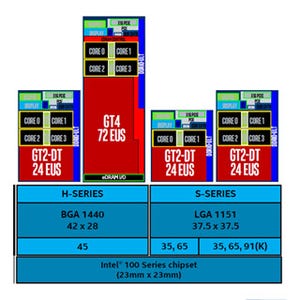

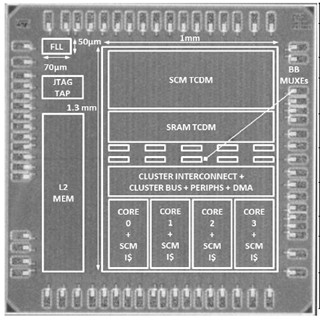

そして、このEUを8個集積し、命令発行機構やL1キャッシュ、L2キャッシュ、テクスチャサンプラ、データポートなどを加えたものをサブスライスと呼ぶ。さらに3個のサブスライスをまとめたものをスライスと呼ぶ。このスライスが増設の単位であり、SkylakeのGPUは1スライス(24EU)、2スライス(48EU)、3スライス(72EU)というバリエーションがある。最大の72EUの製品では8×72=576 MAC演算器を持ち、MAC演算は乗算と加算を同時に実行するので1サイクルに最大1152浮動小数点演算を実行することができる。GPUクロックは発表されていないが、ピーク演算性能は1TFlopsを超えると見られる。

そして、Skylakeチップは、次の図のように、GPU、最大4個のCPUコア、CPUコアとペアになっているL3キャッシュスライス、メモリやI/Oのコントローラなどを含むシステムエージェントをリングインタコネクトで接続するという構造になっている。このリングは32バイト幅で、右回りと左回りのリングがある。

SkylakeではCPUとGPUメモリの共通化を実現

SkylakeのCPUとGPUのページテーブルは共通のメモリ空間を実現するように制御され、CPUのメモリアクセスの場合は、GPUのキャッシュがスヌープされ、GPUのメモリアクセスの場合はCPUのキャッシュがスヌープされ、コヒーレンシ制御が行われる。このスヌープは64バイトのキャッシュライン単位で行われるようになり、従来のページ単位に比べて使い勝手が良くなっている。

Shared Virtual MemoryはCPUとGPUが同じアドレス空間を使うことができ、物理的にも同じメモリを使うので、CPUとGPUの間のデータの受け渡しは論理的にも簡単になったが、それに加えてデータのコピーも不要になり、性能やエネルギー消費の面でも有利になった。これらのCPUとGPUの連係機能の改善により、GPUの強力な浮動小数点演算能力をCPUから使うことがかなり容易になった。

SkylakeではGPUを使うDeep Learningも視野に

Intelは、GPUを描画だけでなく、Computer Visionの処理や、今はやりのDeep Learningの処理にも使おうとしている。Deep Learningで計算量が多いのは畳み込み(Convolution)であり、これは行列積の計算である。行列積はスパコンのランキングに使われるHPLの主要計算であり、GPUの得意な計算である。Deep Learningの場合は疎行列でありデータのアクセスパターンが違うのでHPLの場合ほどうまくは行かないが、それでもGPUに適した計算である。

この分野でのプレゼンスを高めるため、IntelもU.C.Berkeleyの開発したDeep LearningのフレームワークであるCaffeのOpenCL版や代表的なDeep LearningネットワークであるAlexNetの提供などを行っている。ただし、先行するNVIDIAのサポートレベルとはかなり差があるという印象である。