COOL Chips XIXにおいて、IntelのPrincipal EngineerのMichael McCool氏が「New Frontiers in Computing」と題して基調講演を行った。なお、McCool氏から念を押されたが、Skylakeの説明などはIntelの発表資料であるが、将来のコンピューティングに関してはIntelの公式見解ではなく、McCool氏の個人的な見解であるとのことである。その点は読者にも含んでおいて戴きたい。

最初に、McCool氏は、Intelの最新世代のプロセサであるSkylakeについて説明した。Skylakeについては2015年のIDFでも発表されており、新しい情報ではないが、どうしてこのようなプロセサになっているのかという点では、新しいフロンティアがどのようなものかという示唆を含んでいると思われる。しかし、その方向性はIntelの見解ではなく、McCool氏の見解である。そしてこの記事は、筆者の見解もある程度含まれたものになっている。

新しい方向性を盛り込んだSkylakeのGPU

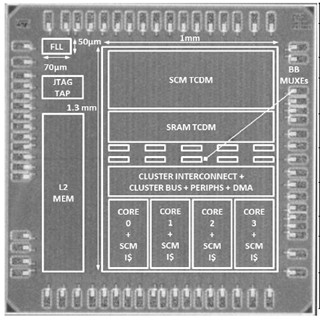

Skylakeは新CPUコア、新GPUコアを使う新世代のプロセサである。CPUコア、GPUコアはモジュラーに設計されており、CPUコアは2個あるいは4個、GPUコアは24EUの基本コアが1個~3個というバリエーションがある。ただし、これは現在発表されている製品での品ぞろえであり、今後、よりCPUコア数の多いサーバ用のチップが出てくるのは間違いない。

後述のように、SkylakeのGPUは、汎用計算を強く意識して機能が拡張されている。従来、サーバ用のチップにはGPUは搭載されていないが、Skylake世代では、サーバ用のチップにもGPUが載るのか、載らないのかは興味深い。

|

|

|

Skylakeは、スケールする範囲の広いプロセサ。TDPは4.5Wから91Wの範囲で、CPUコアは2個か4個、GPUは24EUから72EUのバリエーションがある (この記事のすべての図は、COOL Chips XIXにおけるMcCool氏の基調講演のスライドを引用したものである) |

組込みDRAMを使うMemory Side Cache

従来もEmbedded DRAM(eDRAM)を使った大容量のキャッシュを搭載した製品はあったが、その位置づけはGPUに高バンド幅のメモリを付けるというのが主目的であった。しかしSkylakeでのeDRAMは、次の図のようにCPU、GPU共通に、外付けのDIMMをキャッシュするという位置づけになった。この図では、Last Level Cacheの下にeDRAMのL4キャッシュがあると書かれており、Last Levelという用語と矛盾するが、まあ、それは見逃して置こう。

この構造では、全員が1つのL4キャッシュを共有するので、コア1とコア2のキャッシュに同一アドレスのデータが格納され、一方がそこに書き込みを行って矛盾した状態になるということが原理的に発生しない。従って、キャッシュコヒーレンシを維持する機構は不要である。

筆者の注であるが、それならすべてMemory Side Cacheにすれば良いと思われるかも知れないが、L1キャッシュやL2キャッシュをMemory Side Cacheにすると、1つのキャッシュに全部のコアからアクセスが集中して混雑渋滞が起こってしまう。また、L1キャッシュ、L2キャッシュは実行ユニットの近くに置いてアクセス時間を短くする構造になっているが、Memory Side Cacheにすると、距離が伸びてアクセスが遅くなってしまうので、これらのキャッシュはMemory Side Cacheにはできない。

|

|

|

Skylakeのメモリ階層。コアに含まれるL1キャッシュ、L2キャッシュとチップのCPU、GPUの全コアに共通のLast Level Cache(L3キャッシュ)、L4キャッシュとなるeDRAMのキャッシュが付いている。L4キャッシュはMemory Side CacheですべてのアクセスがL4キャッシュを経由するので、常にコヒーレンシが成立している |

このメモリ側に置かれたキャッシュは、外付けのDIMMと直接対応するので、コヒーレンシ制御の必要は無く、I/Oデバイスやディスプレイエンジンもこのキャッシュを利用することができる。

SkylakeではCPUとGPUは1つのメモリを共用するので、CPUとGPUとの間のデータの受け渡しにデータのコピーを必要としない。これは前世代のGPUでも実現されていたが、今回のGen9では書き込みのスピードが向上している。また、従来は1フレームの描画が終わらないと割り込みができないというような制約があったが、割り込みの掛けられる粒度を小さくし、Preemptionの応答速度を大幅に改善している。これはGPUを描画処理だけでなく、汎用の計算に使おうという方向性を目指していると考えられる。

そして、16bit長の半精度浮動小数点演算で非正規化数をサポートし、ゼロに近い小さな数の精度を改善している。これはディープラーニングなどの計算で半精度演算を使う場合には有効と思われる。このようにSkylakeのGPUは新しいフロンティアを開拓しようとしている。