本連載はHisa Ando氏による連載「コンピュータアーキテクチャ」の初掲載(2005年9月20日掲載)から第72回(2007年3月31日掲載)までの原稿を再掲載したものとなります。第73回以降、最新のものにつきましては、コチラにて、ご確認ください。

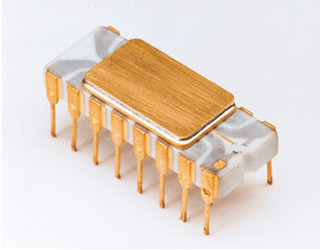

これらの信号を用いて16ビットアダーを構成したのが下の図である。この図では、74S181は、動作を分かり易くするため、4ビットごとのP,G信号を生成する部分とSumを計算する部分を別のボックスとして書いているが、実際の74S181ではこれらのペアが1チップに集積されている。また、74S182はCn+8キャリー、Cn+16キャリーを生成する部分をそれぞれ別のボックスに分割して書いているが、これら4個のボックス全部が1チップに入っている。

この構成で特徴的なことは、Sum回路からのキャリーは使われず、74S182のCn+4~Cn+12信号が、次のSum回路に入力されている点である。74S181のデータシートによるとA、B入力からCn+4信号までの遅延時間は12.5ns、C-inからCn+4信号までの遅延は7nsであるので、Sum回路だけを4個使って、下位のCn+4を次のSum回路のC-inに接続し、最上位のSum回路のCn+4をC-outとすると、最大遅延は7x3+12.5=33.5nsとなる。

一方、P、G信号を用いる場合のクリティカルパス(遅延時間が最大のパス)は、図に赤線で示したパスである。この場合は、74S181のA、B入力からP、G信号までの遅延は8ns、C-inからSumまでの遅延は7ns、そして、74S182のP、G信号からCn+x信号までの遅延は4.5nsであるので、全体の遅延は19.5nsとなる。つまり、P、G回路と74S182を使うことにより、約40%遅延時間が短くなっている。なお、ここで使用した数値はデータシートのTyp(Typicalの略で、平均的な部品の、平均的な使用条件での遅延時間を示す)であり、Max(遅めの部品を高温、低電圧で動かす場合の遅延時間)は1.5倍程度の値になっている。

では、74S182はどうやってCn+4~Cn+16を計算するのであろうか? ここで威力を発揮するのがP信号である。Cn+12を例にとると、Cn+12が"1"となるのは、次の4つケースである。

- A,B11-8の加算でキャリーが出る(A,B11-8のG信号が"1")の場合

- A,B7-4の加算でキャリーが出て、それがA,B11-8の加算器を伝搬してキャリーが発生する(A,B11-8のP信号が"1"であり、A,B7-4のG信号が"1")の場合

- A,B3-0の加算でキャリーが出て、それがA,B7-4とA,B11-8の加算器を伝搬してキャリーが発生する(A,B11-8、AB7-4のP信号がともに"1"であり、A,B3-0のG信号が"1")の場合

- キャリー入力され、それがA,B3-0、A,B7-4とA,B11-8の加算器を伝搬してキャリーが発生する(A,B11-8、A,B7-4、A,B3-0のP信号がともに"1"であり、C-in入力が"1")の場合

つまり、Cn+12=G2+G1・P2+G0・P2・P1+Cin・P2・P1・P0 で生成される。なお、この式のP2、G2はA,B11-8、P1、G1はA,B7-4、P0、G0はA,B3-0の74S181のP、G信号を示す。

このように、P、G信号を用いてキャリーを高速に計算するやり方をキャリールックアヘッド(Carry Lookahead)方式と呼ぶ。

第73回以降の記事は、コチラ。