本連載はHisa Ando氏による連載「コンピュータアーキテクチャ」の初掲載(2005年9月20日掲載)から第72回(2007年3月31日掲載)までの原稿を再掲載したものとなります。第73回以降、最新のものにつきましては、コチラにて、ご確認ください。

フルアダーの図を見ると、Sumの計算は2個のXORゲートで実現されており、これ自体は大して時間のかかる処理ではない。従って、問題は、各桁のC-inをどうやって求めるかということであり、各桁のC-inが短い時間で計算できれば、加算器を高速化できる。

下の桁から順に桁上がりを計算しないで上位の桁上がりを早く計算することなど出来るのかという疑問を持たれるかも知れないが、実は、それが出来るのである。但し、こちらは人間が筆算でやるのには向かず、多数の論理ゲートを使って並列に実行するための方法である。

次に示すのはTexas Instruments社の74S181という4ビット単位の演算チップの機能テーブルであるが、M信号がHighの場合は論理演算を行い、M信号がLowの場合はPLUS、MINUSと書かれた加減算行う。なお、AB PLUS (A + *B)というような訳の判らない機能があるが、これらは回路を作ったらそういう機能になってしまったというオマケであり、気にしなくても良い。

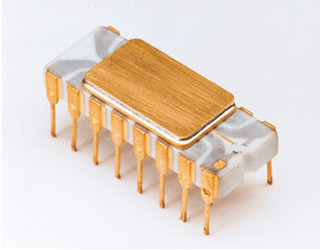

物理的には、74S181は24ピンのDIP(Dual Inline Package)に入っていた。余談であるが、Dual Inlineは2列という意味で、写真では黒いパッケージの左側に一列のピンしか見えないが、右側にも同様に一列のピンがあり、二列にピンが並んでいることから、Dual Inline Packageと呼ばれている。

なお、掲載した写真は40ピンDIPのものであり、24ピンDIPの74S181は高さが半分強になると同時に、パッケージの幅も40ピンのDIPより狭くなっている。

次の図は、この74S181を使って32ビットの高速なアダーを構成する回路を示している。

図の左側の74S181は、S0~3とM入力で前掲の機能テーブルの演算種別を選択し、*A0~3、*B0~3のオペランド入力に対して、これらを演算した結果を*F0~3に出力する。また、Cn入力はキャリーインであり、Cn+4はキャリーアウトである。なお、信号名の上にバーが付いている信号は逆極性で入力することを示しているが、文中ではバーが使えないので*を前置してバーの代わりとする。

これらの信号の意味は見ての通りであるが、それ以外にA=Bと*P、*Gという出力信号が出ている。A=BはA0~3とB0~3が完全に同じという状態と分かるが、74S182に接続されている*Pと*Gは何の役目をする信号であろうか?

実は、これらの信号は、PropagateとGenerateという信号で、P、Gと略記されることが多い。G信号は、キャリーインにかかわらずCn+4にキャリーが発生(Generate)するという状態を示す信号である。そして、P信号は、キャリーインが"1"であれば、それが伝搬(Propagate)してCn+4に"1"が出力されるという信号であるが、厳密に伝搬する状態だけでなく、キャリーインが"0"であってもCn+4にキャリーが発生する状態を含んで良い。つまり、各桁のP信号は、A0~3とB0~3信号の各桁同士のORを取り、そして、それらの各桁のANDを取れば良い。従って、4ビットのグループのP信号は、次の式で表わされる。

- "P = (A0+B0)・(A1+B1)・(A2+B2)・(A3+B3)"

また、キャリーが発生するのは、最上位のA3、B3が共に"1"の場合、A2とB2が共に"1"でA3、B3 が伝搬、A1とB1が共に"1"でA2,B2とA3,B3が伝搬、A0とB0が共に"1"でA1,B1、A2,B2とA3,B3が伝搬の場合であり、G信号は次の式で表わすことができる。

- "G = (A3・B3)+(A2・B2)・(A3+B3)+(A1・B1)・(A2+B2)・(A3+B3)+(A0・B0)・(A1+B1)・(A2+B2)・(A3+B3)"

これらのP、G信号は、下位の桁からのキャリーインとは無関係に、A0~3とB0~3信号の値だけから作ることができるというのがミソである。