本連載はHisa Ando氏による連載「コンピュータアーキテクチャ」の初掲載(2005年9月20日掲載)から第72回(2007年3月31日掲載)までの原稿を再掲載したものとなります。第73回以降、最新のものにつきましては、コチラにて、ご確認ください。

命令フェッチと実行のオーバラップ

更に性能を上げるにはどうすれば良いであろうか? 上のタイミング図を見ると、X1~X4サイクルで命令の実行が終わってから、次の命令のアドレスをAサイクルで送り、Mサイクルで受け取るという動作をしているが、分岐命令でなければ、次の番地の命令を読むという動作が必ず行われる。従って、原理的には、次の命令のフェッチはその必要性が判明した時点から開始して良い。

つまり、MサイクルでPCの値はインクレメントされて次の命令を指しているので、X1サイクルで命令をデコードして分岐命令でないことが判明すれば、このPCの内容をアドレスとしてROMに送り、命令を読んで来ることが可能である。このようにすると、分岐命令でない命令が続いている場合は、次の図のように、3サイクルに1命令のペースで実行することが可能になる。

条件分岐命令の場合は、条件の成立/非成立を判定して分岐するかどうかが決まらないと、次の命令アドレスが決まらない。しかし、MJアーキテクチャではJCN命令は2バイト命令であり、1バイト目のX3サイクルで条件が成立するかどうかを判定でき、2バイト目をROMから読み込めば分岐先のアドレスが得られるので、他の命令と同様に、X2、X3サイクルとA、Mサイクルをオーバラップさせることが出来る。

一方、RAM/IOをアクセスする命令はX2サイクルにアドレスバスを使い、X3サイクルにデータバスを使うので、このオーバラップでは次の命令の読み出しとバスの使用がぶつかってしまう。従って、1サイクル遅らせて、X3サイクルと次の命令のAサイクルがオーバラップするようにする必要がある。このようにオーバラップさせると、前述の10進数の加算のループは次のように実行することが可能になる。

ここで、ADD命令やST命令はRAMをアクセスする命令であるので、次の命令のフェッチはX3サイクルからしか開始できず、2命令目のADDは5サイクル、DAA命令は9サイクル、ST命令は12サイクル、INC命令は16サイクル目からフェッチが行われる。

次のJCN命令は2バイト命令であり、この1バイト目と2バイト目の処理を分けて2段の表記となっている。そして、条件判定が終わり、次のアドレスが確定するのが命令の2バイト目の最後のX1サイクルであるので、L1にジャンプしてADD命令のフェッチが開始できるのは25サイクル目となる。

そうすると、ループ1回に掛かる時間は24サイクルである。つまり、パッケージのピン数を増やしたところまででは42サイクルであった実行時間が、実行のオーバラップを行うことにより24サイクルまで短縮され、1.75倍に高速化されることになる。

このようにオーバラップした実行を行うためには、実行している命令を記憶するレジスタと、次の命令を受け取るためのレジスタを別個に持つ必要がある。また、命令を実行するのと並行して、PCをアドレスバスに送り出す必要があるので、内部4ビットデータバスとは別に、PCをアドレスバスに送るための12ビット幅の内部バスが必要となるなどのハードウェア資源の追加が必要となる。

ここまでやれば、オリジナルの4004プロセサでは96サイクル掛かった処理が、24サイクルと4倍に高速化できる。ということで、ここまでアーキテクチャを進化させれば4ビットプロセサは卒業で、性能を上げるという観点では、4ビットプロセサでこれ以上頑張るよりも、語長を8ビットにした8ビットプロセサに進んだ方が良い。

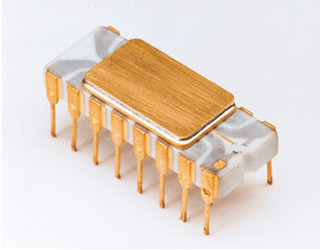

Faggin氏は、この後、Intelで8ビットプロセサである8080の開発を行い、その後、自分の会社であるZilog社を起こし、名作のZ80を開発した。このZ80は16ビットのアドレスバスと8ビットのデータバスを持ち、40ピンのパッケージに入れられている。

命令語は、基本は8ビット、データも基本は8ビットということで、8ビット単位で両者共通の方法でアドレスされ、命令とデータを同じメモリに格納するアーキテクチャとなっている。

基本命令を5サイクルで実行するアーキテクチャであるが、4サイクル後には次の命令のフェッチをオーバラップして開始しており、基本命令は4サイクルピッチで実行することが出来る。

ということで、ここで説明した、4ビット双方バスからアドレス、データバスの分離と幅の拡張、命令フェッチと実行のオーバラップという手法は、実はZ80でも使われていたものである。

なお、ここで説明した拡張では命令ピッチは3~4サイクルであるが、命令実行のオーバラップを更に細かくして、現在の高性能プロセサでは次の命令を1サイクルピッチで実行するパイプライン処理が用いられているが、これについては稿を改めて説明することにして、これで4ビットプロセサのアーキテクチャ設計を終わることにしたい。