本連載はHisa Ando氏による連載「コンピュータアーキテクチャ」の初掲載(2005年9月20日掲載)から第72回(2007年3月31日掲載)までの原稿を再掲載したものとなります。第73回以降、最新のものにつきましては、コチラにて、ご確認ください。

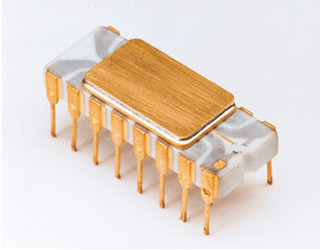

本シリーズのコラムとして、当初は、Hoff氏の思考を辿ってなぜこのようなアーキテクチャになったのかを考察しようと考えていたのであるが、論理的にメリット、デメリットの比較でこう作るべきというアプローチで4004のアーキテクチャを組み立てていくことは出来そうも無い。そこで、4004のアーキテクチャ設計を追体験するのはなく、4004と同程度のトランジスタ数で、かつ、16ピンパッケージに収容できる4ビットプロセサの命令アーキテクチャを新たに設計してみようと思う。これは中々おもしろい課題であり、このような場を提供いただいたMYCOMジャーナルに敬意を表して、これから設計するアーキテクチャをMJアーキテクチャと呼ぶことにする。

1アドレス命令

Sytem/360のような大規模な計算機は32ビットの命令語が基本であり、2つのオペランドを持つ、2アドレスのRR命令やRX命令を作るだけの命令語長があるが、基本命令語長が16ビットの1130や、12ビットのPDP-8では命令語長が短いので演算はアキュムレータとメモリ間で行う1アドレス命令である。

命令語長を長くとると1命令で出来ることが多くなり、高性能を実現しやすいが、一方、実現に必要なハードウェア量は増加する。そこで、小規模なプロセサ向けのMJアーキテクチャでは、比較的短い命令語を使うのが妥当である。PDP-8のように12ビット命令という手もあるが、4ビットバス経由で命令を読もうとすると、読み込みだけで3サイクルが必要となるので、4004に比べて命令の読み込みサイクルが1サイクル余計に必要となり、1命令の実行時間が増えてしまう。各命令が強力になることで一定の処理を行うのに必要となる命令数が減少する効果が期待できるが、4ビットプロセサが使われるような用途では、各命令の実行が遅くなる損失の方が大きいと思われるので、MJアーキテクチャにおいても8ビットの命令語長を採用する。

基本の命令語長を8ビットとすると、オペランドを指定するために使用できるビット数は極めて制限されるので、命令の形式としては、アキュムレータとメモリ間の演算という1アドレス命令のアーキテクチャとする。

レジスタ

次に実行すべき命令を指すPC(プログラムカウンタ)とACC(アキュムレータ)は必須のレジスタであるが、4004では、その他に、サブルーチンコールを行う場合の戻りアドレスを記憶する3段のスタックと、16個の4ビットレジスタからなるインデックスレジスタを持っている。そして、このインデックスレジスタは、ペアにして8ビットでアドレスを指定する場合に使ったり、4ビットのデータを保持するデータレジスタ的に使用したりしている。

しかし、36ビットの資源を使っているスタックをサブルーチンコールだけに使うのは利用効率が低く、また、12ビットのアドレスを指定するインデックスレジスタが8ビット長というのも中途半端であるので、MJアーキテクチャでは、両者を一体化して12ビット長のインデックスレジスタ(IXレジスタ)を4本設けることにしよう。

こうすると、4004ではスタックに12x3=36ビット、インデックスレジスタは4x16=64ビットで合計100ビットであるが、MJアーキでは12x4=48ビットとレジスタに必要なハードウェアを52ビット削減しており、他の部分で多少ハードウェアが増えても、4004と同規模以下に納めることが出来る。

MJアーキテクチャにおいて、ソフトウェアから見えるのは以下のレジスタである。

ここでCYは4004にも存在したアキュムレータの演算結果のキャリーを保持する1ビットのレジスタである。そして、IXCYレジスタは、MJアーキテクチャで新設されたレジスタであり、IXレジスタのインクレメントにより発生したキャリーを保持する1ビットのレジスタである。

MJアーキテクチャでは、IXレジスタは4004のスタックを兼ねる必要があるので、サブルーチンコール命令は戻りアドレスをIXレジスタの最初のエントリであるIX0に書き込み、リターン命令はIX0の内容のアドレスへジャンプする仕様とする。ここまでは、スタックのトップがIX0と名前を変えただけであるが、IXレジスタの内容をメモリに書き出し、メモリから読み出すことが可能な命令を設け、サブルーチンの中でIX0の内容をメモリに退避、復元してやれば、メモリ容量の許す限り任意の深さのサブルーチンコールのネスティング(多重呼び出し)が可能となる。こうすることにより3重の呼び出ししか出来ないという4004の制約を解消することができる。

また、IXレジスタを4004のインデックスレジスタのようにRAMをアクセスする場合のアドレス指定に使える命令を設ける。メモリに格納した16桁の2進化10進数をアクセスする場合のように、順次メモリアドレスを増加してアクセスする使い方が多いが、IXレジスタをPCと一体化すれば、12ビットインクレメンタを共用して、殆ど追加ハードウェアを必要とせずにアドレスの+1が可能となり都合が良い。