本連載はHisa Ando氏による連載「コンピュータアーキテクチャ」の初掲載(2005年9月20日掲載)から第72回(2007年3月31日掲載)までの原稿を再掲載したものとなります。第73回以降、最新のものにつきましては、コチラにて、ご確認ください。

次に、ALU全体の処理とそれぞれのマルチプレクサの選択を表に纏めると次の表のようになる。

このALU動作表からAdd/Subや各マルチプレクサを制御する表を作り、それを生成する回路をNANDやNORゲートを用いて設計することは可能であるが、ここでは次に示すようなROM型の制御信号生成回路を使うことにする。

この回路でDecoderと書いたブロックは16個のレジスタの選択に用いたのと同じ回路で、OPレジスタの4ビットの命令コードが1(0001)の場合は一番上の線が"1"になり、その他は"0"、命令コードが2(0010)の場合は2番目の線が"1"になり、その他は"0"というような信号を生成する。そして、このデコーダはEnable信号が"0"の状態で全ての出力が"0"となるように構成する。

また、Pre-Charge信号が"0"になると、一番上のP-chトランジスタがオンになり、縦方向のビット線はP-chトランジスタを通してVddに接続され"1"となる。この状態ではEnable信号は"0"であり、デコーダの出力は全て"0"となっている。従って、この状態ではビット線との交点に配置されたN-chトランジスタは全てオフであり、ビット線の電位には影響を与えない。

そしてPre-Charge信号が"1"になり、その後、Enable信号が"1"になると、OPregに格納された命令に対応するデコーダの出力線だけが"1"となり、その他のデコーダ出力は"0"となる。その結果、"1"となったデコーダ出力に接続されたN-chトランジスタがオンする。例えば、この図では、命令コード0010(2)の場合はCtl-0とCtl-3 のOR出力線との交点の部分にトランジスタがあるので、この2本のビット線は"0"となり、その他のビット線は(制御信号出力線の寄生容量に蓄積された電荷により)"1"の状態が保たれる。

このビット線の信号がインバータで反転されるので、結果として、Ctl-0とCtl-3の出力が"1"となる。つまり、各Ctl信号は、ビット線との交点にトランジスタが配置されたデコーダの出力のORとなっている。

このようにROM型の制御信号生成回路は、デコーダで各種の条件を作り、それぞれのCtl線をAdd/Sub信号やMX-Y、MX-Aなどの信号に対応させ、制御表に従って交点にN-chトランジスタを配置してORすることにより、任意の条件の制御信号を作り出すことが出来る。

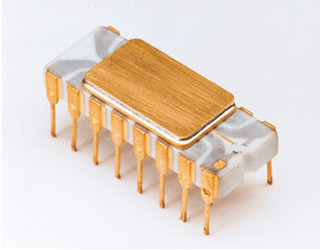

実際、4004でもこのようなROM型の回路が用いられているようであり、2300トランジスタで出来ているというのは、実は全ての交点にトランジスタがあるとした場合のトランジスタ数であり、実際に使われているトランジスタ数は2100個あまりであるとHoff氏は述べている。但し、一般的に、このようなROM型の回路では全ての交点にトランジスタは作っておき、必要なところだけトランジスタのドレインをビット線に繋ぐようになっているので、チップ上に2300トランジスタが有るというのも正しい記述であると考えられる。また、4004は2相式のダイナミック回路を使用しており、Φ1信号でPre-Chargeを行い、Φ2信号でデコーダをエネーブルしていると考えられる。

ALUの制御表では、I/O命令群(OPR=1110)とアキュムレータ命令群(OPR=1111)では複数の命令があり、OPA部により動作が異なるので、それぞれ別個にROM型の制御命令生成回路を作り、OPRの値が1110の場合と1111の場合は、それぞれのROMを使うようにすれば良い。

そして、ALUが動作するのは、各命令の最初の8サイクルのうちのX3サイクルであるので、 X2サイクルに制御信号生成回路を動かせば良いが、命令デコーダの一部としてX1サイクルに制御信号を生成しても良い。

なお、第45回に掲載した4ビット内部バス制御信号発生回路では、デコーダの出力を論理ゲートを用いて組み合わせてバス制御信号を作ったが、このようなROM型の回路でバス制御信号を作っても良い。実は、ALUの制御信号生成回路だけでは200個近い交点の未使用トランジスタは出来ないので、4004では、4ビット内部バス制御信号もROM型の回路で生成されていると考えられる。

ALUユニットで残っているアキュムレータ(ACC)とTempレジスタを次の図に示す。

ACCは4ビット内部バスに接続されるレジスタであるが、他のレジスタと少し違うのは、XCH命令の処理のために、Tempレジスタから直接データを転送するパスを設けている点である。

XCH命令のX3サイクルでは、ACCの内容をインデックスレジスタに転送すると同時に、TempレジスタからACCレジスタにデータを転送する必要がある。しかし、4ビット内部バスはACC→インデックスレジスタのデータ転送に使われてしまうので、バスを使用せずにTemp→ACCの転送を行う必要があり、これを実現するために、ACCのデータ入力に2入力マルチプレクサを設け、データとしてバスの信号を受け取るか、あるいはTempレジスタの値を受け取るかを選択する。Tempレジスタの値を受け取るのはXCH命令のケースだけであるので、XCH命令であるという条件をマルチプレクサの制御信号として用いれば良い。

ALUの最後の部品は、キャリーフラグを保持するYレジスタである。下図に示すように、このレジスタは他のレジスタと違って1ビットで出来ており、他のレジスタとは多少異なる制御を必要とする。

キャリーフラグFFがセットされるのは、ALU制御表でset-CY欄が"-"になっていない場合であり、この条件をROM型制御信号生成回路で作成してset-CY入力に供給する。また、入力マルチプレクサの選択信号も同様に、CY-selectの表に従ってROM型制御信号生成回路で作成する。

これでALUユニットが出来たので、命令レジスタの部分を作れば、4004の論理設計は完了である。