本連載はHisa Ando氏による連載「コンピュータアーキテクチャ」の初掲載(2005年9月20日掲載)から第72回(2007年3月31日掲載)までの原稿を再掲載したものとなります。第73回以降、最新のものにつきましては、コチラにて、ご確認ください。

以上のように、何故CMOS回路が電力を消費するかを見てきたが、2コアにするとプロセサの面積は2倍になり、CLが2倍となる。バスインタフェースや、2次キャッシュなどの2つのコアで共有される部分の面積はさほど増加しないが、2つのコアからのアクセス要求を扱う必要があり、ほぼ2倍忙しくなりαが2倍となる。ということで2コアにすると、常識通り、電力はほぼ2倍となる。

では、なぜ、マルチコアで低消費電力化が出来るかというと、実はマルチコアプロセサでは各コアの動作条件の選択がシングルコアの場合とは異なるからである。マルチコアプロセサでは、シングルコアよりもクロックを下げ、かつ、それに見合うように電源電圧を下げて動作させる。前に述べたように電源電圧とクロックの関係は半導体プロセスや回路設計によるが、単純化したケースでクロックと電源電圧が比例するとした場合には、クロック低下比率の3乗で消費電力が減ることになる。

つまり、2コアでシングルコアと同一の条件で動かせば2倍の消費電力であるが、20%クロックを下げると0.8の3乗で、0.512 x2(コア)=1.024で元のシングルコアと同程度の消費電力で済むことになる。Intelプロセサで見てみると、デュアルコアのPentium D 840は3.2GHzクロックで130W、シングルコアのPentium 4 670は3.8GHzクロックで115Wである。クロック比率は0.842であり、これを3乗して2x115Wを掛けると137WとなりPentium D 840の電力とほぼ一致している。

これがマルチコアであっても、シングルコアのプロセサと比較して同程度の消費電力で実現できる仕掛けである。しかし、これで省電力になっているかというと、話は単純ではない。80%のクロックで動くプロセサコアが2個あると、理想的なケースで両方のコアがフルに動いた場合は最大1.6倍の性能が発揮できる。この場合は、ほぼ同じ消費電力で1.6倍の処理ができるので、明らかに省電力になっている。しかし、最悪、片方のコアしか使えない処理ではどうなるであろう。ほぼ同じ消費電力で0.8倍の処理性能では効率が悪いが、片方のコアしか使わない状態では遊んでいるコアの動作率αは低下するので、消費電力も下がり、多分、あまり損をしないレベルになると思われる。また、片方のコアが長時間遊ぶ場合は、スリープ状態にすれば更に電力消費を抑えられる。このように考えると、実質的にはデュアルコアにすることにより省電力化ができると考えて良い。

では、マルチコア化のデメリットは無いのであろうか? コアを複数集積するのであるから、まず、考えられるのはチップ面積の増大である。考えようによってはマルチコアのような並列化による低電力化は、物量(=チップ面積)というコストを払って電力削減を買っているという面がある。IntelやAMDなどの半導体メーカとしてはチップが大きくなり製造コストが上がるのは不利益であるが、電力を抑えて性能を上げていくためにはやむを得ないということであろう。

また、ユーザから見ると、マルチコアで総合性能は上がるが、単一のコアしか使えないような処理ではシングルコアに比較して性能が下がることになるというデメリットがある。しかし、消費電力が限界に来ているので、良いとこ取りは出来ずどちらかを選ぶ必要があるが、どちらが良いかは使い方に依存するので、メーカーはシングルコアでクロック高めとデュアルコアでクロック低めという両方のプロセサを提供し続けている。

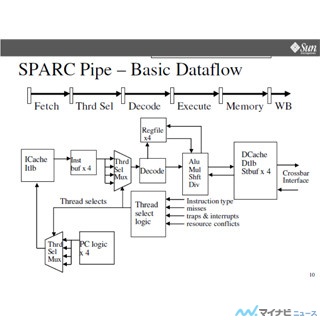

多数の処理を並列に実行する必要があるウェブサーバなどでは、仕事はふんだんにありマルチコアでも十分に使いきることができる。従って、デスクトップと違って、サーバではマルチコア化が急速に進むと考えられる。また、ウェブサーバなどでは一定時間内に応答を返すことが出来れば良く、それに間に合えば、個々のプロセサの性能はそれほど高くなくても良い。このような用途ではデュアルコアと言わず、もっとコア数を増やした方が電力効率が良い。この考えを推し進めたのがSunから登場間近といわれるNiagaraプロセサである。Niagaraは小さめのプロセサコアを8個集積し、そのそれぞれのコアが4スレッドを並列実行し、1チップで32スレッドを並列的に走らせることができるプロセサであるが、これについては何れ稿を改めて述べることにしたい。