信頼性と品質基準

チップレットの品質とは、製造時の状態を指している。チップレットは、モノリシックSoCと同様に、製造プロセスにおいてアプリケーション分野ごとに特定の品質基準に従い、パフォーマンスや機能などの側面をカバーしている。

厳格なテストにもかかわらず、一部の欠陥はその過程で検出されずに最終的なチップレットに「漏れ」てしまう。いわゆる「テスト漏れ」である。携帯電話などの民生用電子機器で許容される欠陥の一般的な数は 100dppm(100万個あたりの不良部品数)である。これは100万個のチップレットごとに100個の不良品が許容されることを意味している。逆に、自動車は最も厳格なアプリケーション分野で、顧客は「0dppm」(実際には1桁のdppmに相当)を求めている。これは、自動車の電子機器が安全にとって重要であることが多いためである。例えばテスト漏れにより正当な理由もなくエアバッグが開いてしまうと、ドライバーが事故を起こす可能性が生じることとなる。また、カーラジオの問題が些細なことのように見えても、ラジオが再生されなければ、最終顧客は新車の納入を断るだろう。その他の要求の厳しいアプリケーション分野としては、同様に命を預かる航空電子工学や医療も挙げられる。

チップレットは製造後にテストされ、信頼性を確保するために加熱、冷却、熱衝撃振動テストなど、動作寿命中の潜在的な故障メカニズムを特定する。

テストのための設計標準

チップレットベースの集積回路は個別のコンポーネントから組み立てられるため、通常、統合システムとして製造されるモノリシックSoCよりも多くの潜在的なテストの機会がある。たとえば、接合前に個々のチップレットが仕様を満たし、欠陥がないことを確認するためにチェックされる。その後、相互接続の整合性と信頼性がテストされる。最後に、チップレットが組み立てられた後、設計全体が評価される。

2.5Dおよび3Dチップレットベースの設計の電気テストにおける大きな課題の1つは、設計のすべてのチップレットにテスト信号を送り、応答を読み取ることである。さまざまなソースのチップレットにテストアクセスの互換性があることを保証するために、imecはテストアクセス用の3D-DfTの「IEEE Std 1838」の標準化を開始した。

たとえば、4つのチップレット(1つ=下部、4つ=上部)のスタックでチップレット番号3をテストするには、チップレット番号1と2に「テスト用設計」(DfT)構造が必要である。これらのダイを介したテストデータの送受信の転送を確実にするためである。チップレットはさまざまなベンダーから提供される可能性があるため、通信を確実に行うにはこれらのDfT構造を標準化する必要がある。2020年以降、IEEE Std 1838は、電子設計自動化(EDA)を専門とするすべてのソフトウェア企業が従う標準DfTを規定している。

-

図4:3つのチップレットを備えた3Dスタックの断面。IEEE Std 1838では、さまざまなチップレットにテスト設計要素を導入して「エレベーター」を形成し、テストによる応答がスタック内のすべてのチップレットに到達できるようにした

相互接続のテストの改善

これまで企業は独自の専用設計フローとツールを使用して、チップを最初から最後まで開発してきた。しかし、チップレットベースのアプローチでは、異なるベンダーのチップレットが効果的に接続するためには同じ言語を使用する必要がある。つまり、標準化が必要となる。「Universal Chiplet Interconnect Express(UCIe)」は、ダイまたはチップレット間の相互接続に重点を置いた標準であり、競合企業の境界を越えて広がっている。

現在の相互接続テスト方法は、ハードオープンおよびショート欠陥を対象としており、k個の相互接続に対して 2×[log2(k)]のテストパターン数が必要である。最近、imecは、弱い欠陥バリアント(高抵抗ショートおよび低抵抗オープン欠陥)もカバーすることでより効果的な、改良された相互接続テスト生成方法(E2I-TEST)を提案した。この方法では、隣接する相互接続間のショートのみを考慮することでテスト効率が向上する。さらに、必要なテストパターンは8×[log2(4)]=16個だけなので、テストパターン数を相互接続数kへの依存性から切り離すことができる。

-

図5:imecの相互接続テスト生成方法「E2I-TEST」。マイクロバンプ欠陥の抵抗バリアントもカバーしている。これらのSEM写真には、考えられるすべてのオープン欠陥とショート欠陥の例が示されている (出所:imec)

結論

半導体プロセスの微細化がきわめて複雑となり、設計および処理コストが上昇するにつれて、自動車業界のモデルやタイプの多さを考えればわかるように、小規模アプリケーションでは、最先端のテクノロジーノードで専用のSoCを開発することがより困難になる。機能とテクノロジーノードを異なるチップレットに分離すると、最先端プロセステクノロジーで巨大なチップを開発するよりもコスト効率が高く、スペースとパフォーマンスの面でメリットを得ることができるようになる。

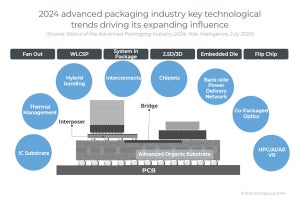

また、モジュール方式は、マルチチップパッケージの複雑さとコストに対する解決策を提供するが、このパラダイムシフトは特定の技術的課題をもたらしている。サイズは1つの課題にすぎない。チップレット研究の大部分は、相互接続を小さくすることや、チップレットをいかにまとめるかといったさまざまなコンセプトの探求に費やされている。チップレットを積み重ねる場合、熱の問題と電力供給(背面電力供給ネットワークなどの新しいアーキテクチャによって対処)が重要になる。今後とも、異なるチップレット間の互換性と通信を保証するために、さらなる標準化の取り組みが必要である。

参考文献

- Why are chiplets attracting the attention of the automotive industry?

- Automotive semiconductor technologies - Tap into imec’s expertise to speed up your development of components for tomorrow’s supercomputers on wheels.

- Wafer-to-wafer hybrid bonding: pushing the boundaries to 400nm interconnect pitch

- Backside power delivery

- New standard allows stacked dies in 3D integrated circuits to connect with test equipment

- Imec and Cascade Microtech Develop First Automatic Probe System for Advanced 3D Chips

- Generating Test Patterns for Chiplet Interconnects: Achieving Optimal Effectiveness and Efficiency

- IEEE Std P3405: New Standard-under-Development for Chiplet Interconnect Test and Repair

本記事はimecが同社Webサイトならびに「3D InCites」に寄稿した記事「Chiplets: Piecing Together the Next Generation of Chips (Part II)」を翻訳・改編したものとなります

エリック・ベイン(Eric Beyne)

ヘルト・ファン・デル・プラス(Geert Van der Plas)

エリック・ヤン・マリニッセン(Erik Jan Marinissen)