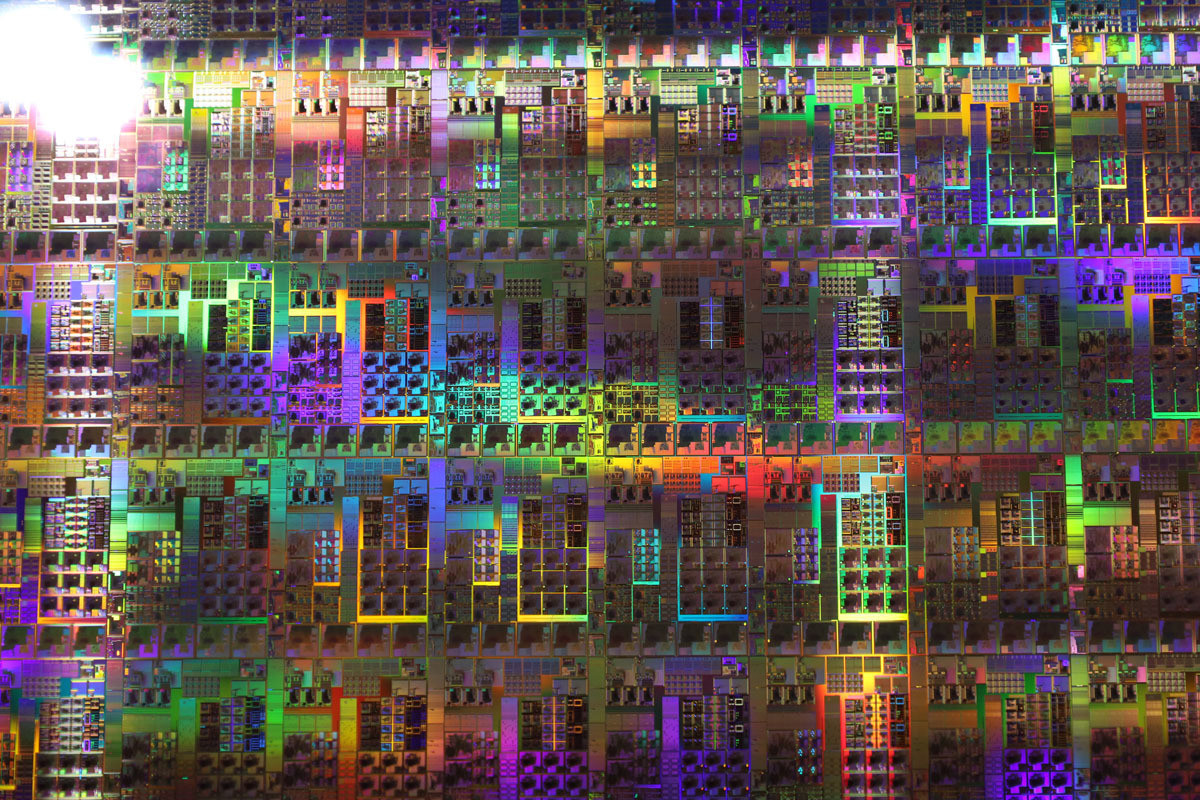

imecのA.Vandooren氏らはVLSIシンポジウム2022にて、薄膜層転写を可能にする3つの異なるプロセスを評価したことを報告している。この論文では、トップ(完全空乏型シリコンオンインシュレータ:FD-SOI)デバイスとボトム(バルクFinFET)デバイスの両方のデバイス性能に対するさまざまなプロセスオプションの影響が検討されている。

堀口氏は「コストの観点から特に有望なのは、Soitecの低温スマートカットフローである。これはバルクドナーウェハを使用して、低温での薄層分割を可能にする。このアプローチの利点は、ドナーウェハを再利用できるため、費用対効果の高いソリューションになることである。他の2つのアプローチはどちらも、研削による基板の除去とSiエッチバックに依存しており、ドナーウェハの再利用はできない」と述べている。

さらなる最適化により、層転写後に低温スマートカットで処理された最上位デバイスは、劣化した電気的性能から回復することが示されている。堀口氏は「低温処理が最適化していないと、デバイスの電子移動度が低下する。Soitecはさらなるソリューションを開発し、Siチャネルの結晶品質を向上させる低温処理工程を最適化することで移動度低下を回復できることを示した。このアプローチの費用対効果を考えると、新しく開発されたプロセス条件を備えたスマートカットは、シーケンシャルCFETプロセスフローでレイヤー転送を実行するための有効な選択肢であると考えている。これは、CFETを超えた3Dシーケンシャルスタッキングアプリケーションを可能にするフローを提供する。たとえば、メモリオンロジックまたはロジックオンロジックの3Dシーケンシャル統合などである」と述べている。

-

図6 低温スマートカット層転写アプローチにおける電子有効電界移動度と反転電荷の比較。最適化されたプロセス条件とレファレンス(概念実証)プロセス条件を比較した。このグラフは、選択B(紫色)の移動度の向上を示している。これは追加の低温熱処理工程を示している(VLSIシンポジウム2022で発表)

これらのテストデバイスを使用して、機能的なインバータチェーンによって検証された、上部と下部のデバイス間の良好な電気的相互接続性を示したほか、最上層のpMOSデバイスのゲートスタックの信頼性は、前述のように、水素プラズマ処理工程を追加することによって維持されることを確認した。

堀口氏は、「このアーキテクチャはまだ究極のCFETプロセスではないことを強調したい」とするほか、「たとえば、想定されているシーケンシャルCFETアーキテクチャでは、下部デバイスの金属相互接続層(M1B)がない。Vandooren氏によるVLSIシンポジウムの論文に示されているテストビークルは、シーケンシャルCFETおよびその他の3Dシーケンシャルスタッキング実現のための主要モジュールとして、改善されたレイヤ転送を実証するために使用された。将来的には、最適化された集積ステップに向けて取り組み続け、最終的には真のシーケンシャルCFETを実現したい」としている。

|

|

堀口直人

imecのロジックCMOSスケーリングプログラムディレクター。1992年に富士通研究所入社。1999年まで富士通研究所やカリフォルニア大学サンタバーバラ校にて半導体ナノ構造を用いたデバイス開発に従事。2000年から2006年まで、富士通でインテグレーションエンジニアとして90-45nm CMOS技術の開発に携わった後、2006年よりimec勤務。以降、世界中の産業パートナー、大学、研究機関とともに高度なCMOSデバイスの研究開発に携わっている。現在の注力事項はCMOSデバイスの1nmテクノロジノード超のスケーリング |

|

|

Julien Ryckaert

imecのロジック微細化担当副社長。2000年にベルギーのブリュッセル大学(ULB)で電気工学の修士号を取得、2007年にはブリュッセル自由大学(VUB)で博士号を取得。2000年にミクスドシグナル設計者としてimecに入社、RFトランシーバ、超低電力回路技術、およびアナログ/デジタルコンバータの設計に従事。2010年に3D ICの設計を担当するプロセス技術部門に異動。2013年以降、先進CMOSテクノロジノード向けの設計技術同時最適化(DTCO)プラットフォームを統括。2018年に、3nmテクノロジノードを超えるスケーリングとCMOSの3D スケーリング拡張に焦点を当てたプログラムディレクターに就任 |