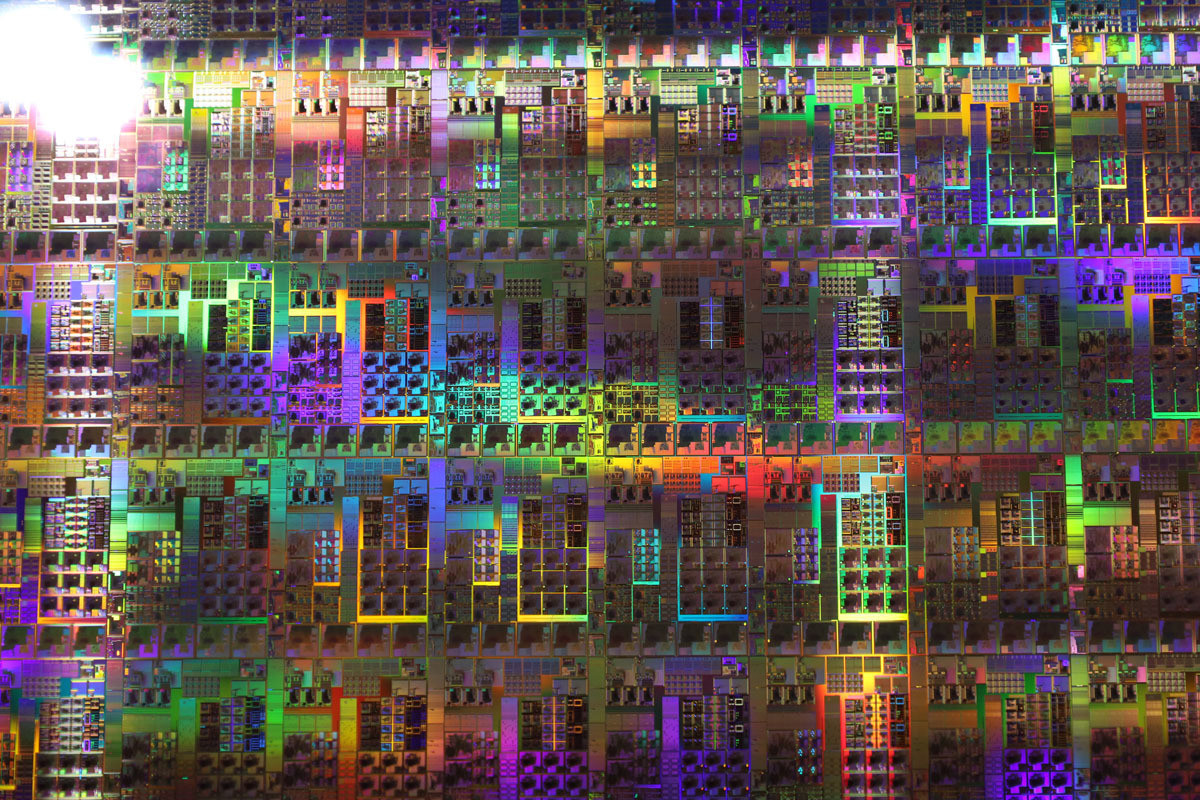

ベルギーimecは、トランジスタ・アーキテクチャとして、現在使われているFinFETからナノシート(2024年)、フォークシート(2028年)を経てCFET(Complimentary Field Effect Transistor:相補型電界効果トランジスタ)(2032年)に至る長期ロードマップを発表している(図1、図2参照)。

CFETは、4Tセル(4本のメタル配線トラックが走る基本セル)設計でフォークシートトランジスタよりも性能が優れているため、1nm未満のロジックテクノロジノードにとって魅力的なデバイスアーキテクチャ(構造)の有力候補になっている。imecは、CFETデバイスを製造するために2つの異なる集積方式-モノリシック方式とシーケンシャル方式-を検討している。

imecのCMOSスケーリングプログラムのディレクターを務める堀口直人氏と、imecのロジックテクノロジ担当副社長であるJulien Ryckaert氏が、双方の集積方式の比較評価を実施し、低温層転写プロセスを含むシーケンシャルCFETの最適化されたプロセスフローの提案を行っている。なお、これらの検討結果は、2022年に開催された「IEEE VLSI Symposium on Technology and Circuits(VLSIシンポジウム2022)」で2つの論文として発表されている。

CFETがロジックテクノロジロードマップに登場

2021年のVLSIシンポジウムで、imecはフォークシートデバイスアーキテクチャを導入したことを報告し、ナノシートトランジスタファミリのスケーラビリティを1nmノードを超えて拡張した(図3)。

このフォークシートデバイスでは、n型トランジスタと p型トランジスタ間の薄い絶縁膜を介して縮小されるため、従来のGate-All-Around(GAA)ナノシートデバイスよりも実効チャネル幅を大きくすることができる。そして、これはトランジスタの駆動電流(またはDC性能)向上に役立つ。さらに、n型トランジスタとp型トランジスタの間隔を小さくすると、スタンダードセルの高さをさらに減らすことができ、スタンダードセルが4T(トラック)の設計に向かって徐々に押し進められる。これは、4つのイントラセル・メタルラインがスタンダードセルの高さの範囲に収まることを意味している。

しかし、4Tセル設計と16nmほどの狭い金属配線ピッチを採用した場合、フォークシートは狭くなりすぎて、必要なパフォーマンスを出すのに苦労する。この課題は、imecのP. Schuddinck氏らによってVLSIシンポジウム2022の論文で指摘されている。そして、それがCFETの登場を促しすことにつながった。

Julien Ryckaert氏は、「CFETアーキテクチャは、n- MOSおよびp-MOSデバイスが互いに積み重ねられている。スタッキングにより、セルの高さを考慮する上で n型とp型トランジスタの間隔が取り除かれ、実効チャネル幅、つまり駆動電流を最大化できる。また、結果として得られる面積の増加を使用して、トラックの高さを4T以下に抑えることができる」と述べている。

(次回に続く)

|

|

堀口直人

imecのロジックCMOSスケーリングプログラムディレクター。1992年に富士通研究所入社。1999年まで富士通研究所やカリフォルニア大学サンタバーバラ校にて半導体ナノ構造を用いたデバイス開発に従事。2000年から2006年まで、富士通でインテグレーションエンジニアとして90-45nm CMOS技術の開発に携わった後、2006年よりimec勤務。以降、世界中の産業パートナー、大学、研究機関とともに高度なCMOSデバイスの研究開発に携わっている。現在の注力事項はCMOSデバイスの1nmテクノロジノード超のスケーリング |

|

|

Julien Ryckaert

imecのロジック微細化担当副社長。2000年にベルギーのブリュッセル大学(ULB)で電気工学の修士号を取得、2007年にはブリュッセル自由大学(VUB)で博士号を取得。2000年にミクスドシグナル設計者としてimecに入社、RFトランシーバ、超低電力回路技術、およびアナログ/デジタルコンバータの設計に従事。2010年に3D ICの設計を担当するプロセス技術部門に異動。2013年以降、先進CMOSテクノロジノード向けの設計技術同時最適化(DTCO)プラットフォームを統括。2018年に、3nmテクノロジノードを超えるスケーリングとCMOSの3D スケーリング拡張に焦点を当てたプログラムディレクターに就任 |