新しいクルマ用SoCを開発するためのコンソーシアム「ASARA(Advanced SoC Research for Automotive)自動車用先端SoC技術研究組合」の中身が少しずつ明らかになってきた。

3月29日に開催した説明会において、基本的には、チップレットを中核に据え、自動車メーカーが持つ電子システムのプラットフォームにするための集積回路となると説明した。なぜそれが可能になるのか。競争と協調の線引きはどうなるのか?。

ASAR理事長でトヨタ自動車のシニアフェローでもある山本圭司氏(図1)は、「半導体がクルマの性能を決める時代に入ってきた。自動車向けの半導体やコンピュータ、電子システム、ソフトウエアなどこれまではそれぞれが開発してきたものをOEM(自動車メーカー)がまとめる形だったが、それを、1チームとして最適なものをそれぞれに提示して作っていく方向にしたい」と述べている。

クルマの電子システムでは、これまでのようなOEM、ティア1、ティア2というような垂直統合の仕組みがもはや崩れている。OEMは、ティア2の半導体メーカー、さらにはティア3のファウンドリと直接話をしなければならなくなってきたからだ。従来の垂直システムだと、OEMとなる自動車メーカーは、ファウンドリとは遠くなりすぎて、中核情報が遅れてしまうきらいがあった。だから、みんなが1チームとなってクルマの開発を進めていかなければならなくなったのである。

電子システムの鍵を握るのはもちろん半導体であり、もはやかつてのような単なる一部品ではなくなった。自動車の頭脳というべき中枢部を司る重要なテクノロジーとなった。自動車メーカーはもはや半導体なしで、次世代のクルマを語ることはできなくなった。そこで自動車各社とも使える技術としてチップレットをはじめとする先端パッケージング技術に目を付けた。

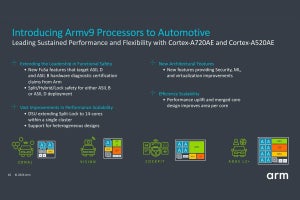

先端パッケージング技術ではチップレットやチップを共通のサブストレート上に置き、SiP(System in Package)としてICを構成する。ある自動車メーカーでは、例えばハイエンド向けのチップを4分割してSoCチップレットとし、ローエンドには1個のチップレット、ミッドレンジには2個のチップレットを使うことで(図2)、車種ごとにSoCを設計し直す必要をなくすことができる。このため開発期間を短縮できる。またメモリもそのパッケージ内に収めておけばSoC(その中のCPU)との距離が短くできるためシステム性能が高まり、消費電力が下がる。

またチップレットという小さなチップにすれば歩留まりが上がるというメリットもある。CPUのプロセスノードとメモリや他の周辺回路チップレットやチップのプロセスノードが違ってもかまわないという柔軟性も上がる。

2024年3月29日にはASRAに対して、NEDO(新エネルギー・産業技術総合開発機構)の掲げる「ポスト5G情報通信システム基盤強化研究開発事業/ポスト5G情報通信システムの開発(助成)」に応募、パスしたプロジェクトとして2024年度分となる10億円の研究開発費が提供されることが決まった。

ASRAがプロジェクトチームとして開発すべき研究課題は、チップレットを作製・実装する技術だけではない。SoCでは必ずCPUが必要で、その上にソフトウエアが走るコンピュータとして動作をする。ただし、各SoCがやり取りをするメモリが共有されていなければ他のSoCとやり取りできなくなってしまう。このため「各SoCが持つメモリ内容を全てのCPUが共有できるというキャッシュコヒーレンシー技術を新たに開発していく必要がある。機能安全やリアルタイム性の技術も必要で、これらの技術を開発、提案し、標準化へとつなげたい」と専務理事の川原伸章氏(図3)は語っている。

また、厳しい環境に晒されるクルマの信頼性に関しても、このSiP半導体に使う材料技術を含め、開発していかなければならない。このため2024年度から5年間に渡り研究開発を続けていく。先ほどの10億円は2024年度分であり、ステージゲートの審査は伴うものの、2025年度以降も助成が行われることが予想される。

SoC内のCPUは、OSやミドルウエア、アプリケーションなどのソフトウエアが必要だ。また、クルマではOSにリアルタイムOS(RTOS)も用意する必要がある。CPUでもArm、RISC-Vなどの選択肢がある。このためOEM各社が共通のCPUやSoCを作るのではなく、それらは競争することになる。OEMによっては独自のSoCが欲しいというケースがあるだろう。

となると、SoCそのものの仕様は各社まちまちだが、その各社内では統一されたSoCを使うことで、競争しながらも開発期間の短縮が可能になる。ただし、チップレットSoCを使うという点では共通し、しかもメモリのコヒーレンシーを追求するという点でも共通な技術を開発できる。また、チップレットではチップレットやチップ同士を接続する端子のサイズと距離・ピッチなどは共通化しておく必要があるため、UCIe仕様に準じるとしている。

OSもRTOSを共存させるという点では共通かもしれないが、どのOSを使うという点では各社で競争することになる。もちろんミドルウエアは各社バラバラだろうが、その上で走るアプリケーションソフトウエアもバラバラになる。ソフトウエア開発での共通点を今後、探していくことになるだろう。ソフト開発者が各社とも大量に必要になる。