パワー半導体の巨人Infineon Technologiesは、従来のシリコンのパワーMOSFETにおいても新型パッケージで使い勝手をよくする技術を開発している。MOSFETのソースをプリント回路基板側に取り付ける技術や、パッケージ表面を放熱する技術など新しいパワー半導体技術を最近、発表している。

これまでのパワートランジスタの常識を覆す、パワーMOSFETのパッケージング技術を紹介しよう。同社が「OptiMOS」と呼ぶ25V~150VのパワーMOSFET技術は、オン抵抗(Ron)が小さいために効率が高く、電力密度も高い。しかもコスト的にも合理的だ。

パワーMOSFETのシリコン構造は、シリコン基板側がドレインで、表面側にソースとゲートを設けた構造をとっている。この基本構造で、チップをパッケージに実装しようとすると、ドレイン側が下になり、ソース側が上に来る。トランジスタを放熱する場合にはシリコン基板側のドレインに放熱板を設けることが多い。ただ、表面実装のパワートランジスタでは、ドレインをプリント回路基板に実装しその裏側に放熱フィンを設置することが多い。

ドレインには大きな放熱板を設けられない場合もある。例えばハーフブリッジ回路を作る場合、ローサイドスイッチの役割を果たすnチャンネルMOSのドレインが、ハイサイド側のpチャンネルMOSのドレインと接してノードとなるが、このノードの面積を大きくすればノイズの影響を受けやすくなる。電位がフォローティングになるときが来るからだ。このため、ドレインの放熱板を大きくできなかった。

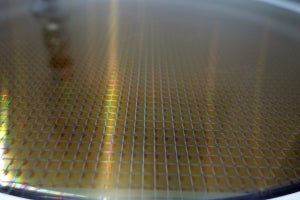

今回ドレインがシリコン基板側になるMOSのチップ構造を変えないまま、ソース側の電極をパッケージ内部で下側(リードフレーム側)にフェイスダウンしてパッケージに実装すると、ダイの面積を少し大きくすることができる。このことによって、オン抵抗を30%ちいさくでき、耐圧が25Vの製品ではわずか0.5mΩと小さなオン抵抗を実現できた。これをわずか3mm×3mmのPQFNパッケージに実装している。

ソースダウンのパッケージをプリント回路基板に実装する場合には、ソース電極とプリント回路基板のサーマルビアを何本も取り付けることによって、熱抵抗を減らすことができる(図1)。つまり、ソースは接地されるため、放熱の面積を大きくしてもノイズには関係なくなる。同じ製品ファミリで比較すると、熱抵抗は従来のドレインダウンだと1.8K/Wだったのが、ソースダウンによって20%低い1.4K/Wという熱抵抗に大きく下がった。

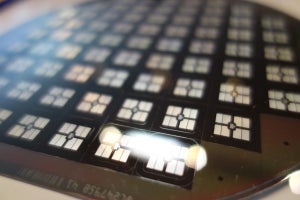

Infineonはもう1つ、使い勝手の点から冷却しやすいパッケージを提案している。これは表面実装パッケージの表面側に放熱板を取り付けられるようなパッケージである。ドレイン電極側に放熱板を取り付ける構造ではあるが、ドレイン電極を大きくする必要はない。従来の表面実装できるパワートランジスタのパッケージ(TOLL:TO LeadLess)は、プリント回路基板に搭載した後、回路基板の裏に放熱板などを取り付けなければならなかった(図2の左)。これでは熱が伝わる距離が遠くなるため熱抵抗が上がり、トランジスタに大電流を流せなくなってしまう。温度が上がりすぎるためだ。

今回は、リードフレームにシリコン基板のドレイン電極を取り付けながらも、ゲートとソースのリード端子を従来のガルウィングの曲げ方とは逆に曲げて、下側にあるドレイン電極を上側にくるようにひっくり返すのだ(図2の右)。

ただし、nチャンネルMOSFETのドレインにはプラスの電圧を印加するため、表面積の大きな放熱フィンとドレイン電極との間に電気的に絶縁する必要がある。通常はTIM(thermal interface material)材料を挟んで絶縁する。しかも熱をよく逃がすために熱抵抗の低い材料が望まれる。一般に、金属のように熱伝導の良いものは電気伝導も良い。しかし、このTIMは電気伝導が悪く、熱伝導だけ良いという材料が求められる。

このTOLTパッケージは、熱のルートがドレインからTIMを通して直接放熱フィンにつなげられるため、熱抵抗を小さくできる。このためトランジスタの電力を20%以上増やすことができるという(参考資料1)。扱える電力が大きいと、これからの48V系のマイルドハイブリッドでは有利になる。ファンやポンプなども48V電源に移行すると、40Aや100A程度のいろいろなモータ駆動のアクセサリに使える効率の高いパワートランジスタとして期待される。おまけに、プリント回路基板の裏側に放熱板を向ける必要がないため、コンデンサや抵抗などの受動部品を裏面に載せられるというメリットもある。

参考資料