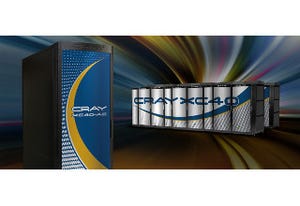

Cray X-MP

Seymour CaryはCray-1の開発後は、次の野心作であるCray-2の開発を行った。しかし、Cary-2の開発は難航して遅れており、それだけに会社の命運を預けるのは危険と見て、 Cray Researchは並行して「Cray X-MP」というマシンの開発を行った。そして、1982年にCray X-MPを発表した。一方、Cray-2の発表は1985年であるので、保険でX-MPを開発したのは正解であった。

MPが付いているように、X-MPはCrayとしては初めてのマルチプロセサのスパコンであり、単純にいうと、Cray-1を最大4台繋いだようなマシンである。Cray X-MPの主任設計者はSteve Chenである。

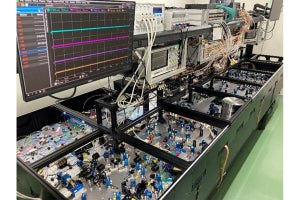

Cray X-MPはCray-1をベースにしたマシンであるので、基本的には、電源や冷却系を入れたベース部分とロジックやメモリを入れたタワーでできている。なお、Cray-1は2ゲートのECL ICを使っていたが、X-MPでは最大16ゲートのECL MSIを使っており、4個のプロセサをCray-1と同じ12カラムのシャシーに収めている。

さらに、I/Oサブシステムに4カラム、SSDに4カラムというように90度の円弧のシステムが並んでいる。

メモリもCray-1では1Kbitのチップであったが、X-MPでは4Kbitのチップを使っており、こちらも体積は小さくなっている。ただし、基本構成でのメモリ容量は2M語に増加し、4CPUシステムでは最大8M語のメモリとなっている。

X-MPのクロックは、1982年のマシンでは9.5nsであったが、その後、8.5nsに高速化されている。そして、1984年には2CPUと4CPUの構成がサポートされた。4CPUのX-MP/48は800MFlopsの性能をもっている。

もちろん、X-MPも16ゲートのゲートアレイを使いCPU 1個は小さく作られていて、Cray-1と比べるとクロックも上がっているのであるが、筆者としては、この写真を見ると、Cray-1、2、3のように、配線遅延を最小にしてクロックを上げて高性能を目指すというCrayの思想(執念?)とは一致しないという気がする。

Seymour Crayの設計は製造性や保守性を犠牲にしており、良いトレードオフであるかは議論のあるところであるが、何としても高性能を目指すというCrayの思想は明確である。

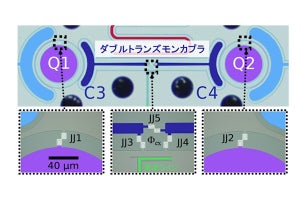

X-MPの構成は、次の図1.54のようになっている。最大4台のCPUが、共通のセントラルメモリと共通のCPU I/Oに繋がっており、4個のCPU間にはCPU間の通信と制御と書かれたブロックがある。

そして、メモリに接続されたI/Oサブシステムから磁気テープやディスク、フロントエンドなどが繋がり、高速の半導体ディスクは直接メモリにデータ転送できる構造になっている。

プロセサの機能として大きなエンハンスは、セントラルメモリがプロセサごとに2つのReadアクセス、1つのWriteアクセスと1つのI/Oアクセスができるポートを持った点である。また、8.5nsクロックのシステムでは、メモリのサイクルタイムはCray-1の50nsに対して、34nsに高速化されている。

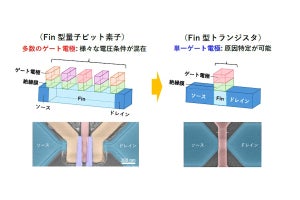

もう1つの改善は、メモリアクセスでScatter/Gatherがサポートされた点である。Cray-1ではメモリの連続アドレスの領域にベクタ処理されるデータを並べて格納して置く必要があったが、X-MPでは飛び飛びのアドレスに格納されたベクタ要素を読むギャザーやベクタ要素を飛び飛びのアドレスに格納するスキャッタがサポートされた。

行列をアクセスする場合、行方向の要素は連続アドレスに格納されているとしても、その場合、列方向のアクセスは飛び飛びのアドレスになってしまう。また、処理によっては対角線方向の要素を読むという場合もあり、これも飛び飛びのアドレスのアクセスになる。Cray-1では、まず、並べ直しを行って連続アドレスに格納してからベクタ処理を行う必要があったが、X-MPでは一定間隔で飛び飛びのアドレスに要素が散らばっている状態でベクタ処理ができるようになった。

図1.55はCPUのブロック図で、Cray-1のCPUから基本的に変わっていない。

(次回は10月26日の掲載予定です)