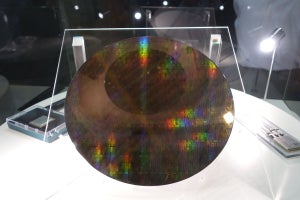

Rapidus(ラピダス)は12月11日、半導体設計向けEDAベンダのSynopsysと、プロセス感度やばらつきの新しいモデル化により設計のサイクルタイムを短縮するソリューションを共同で開発することで合意したことを発表した。

今回の協業の一環としてSynopsysでは、同社のAIベースEDAツール群を活用した最先端設計フローを開発し、ラピダスの2nm GAAプロセスに対応する幅広いIPポートフォリオを提供することで、設計と製造の同時最適化を推進し、アジャイルな設計を可能にするラピダスのDesign for Manufacturing and Co-Optimization(DMCO)コンセプトの具体化を支援するという。

一般的に半導体設計におけるIPライブラリのキャラクタリゼーションは、PDKや製造プロセスがアップデートされるたびに行う必要があるため、タイミングモデルを生成するために、2~3カ月ほどの期間を必要とするが、今回の協業にもとづくDMCOのワークフローでは、PDKや製造プロセスがアップデートされた際に、センシティビティ・ライブラリを用いた機械学習(ML)ベースのタイミングモデル生成ツールであるPrimeShieldを含むSynopsysのAIベースEDAソリューションを活用することで、そうした問題を最小化することが可能となり、プロセスの更新とPDK更新に合わせたロジックおよびメモリのタイミングモデル作成に必要な時間を数日に短縮することを可能になるという。また、ラピダスの短TAT製造によるシリコンデータを用いたキャリブレーションにより、モデルの精度が上がり、設計の収束を加速させることができるようになるともしている。