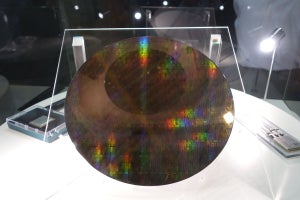

Rapidus(ラピダス)は12月11日、Cadence Design SystemsとAIドリブンのリファレンス・デザイン・フローと幅広いIPポートフォリオの提供で協業すると発表した。

この協業に基づき、ラピダスの2nm GAA製造プロセスと裏面電極(BSPDN:Backside Power Delivery Network)技術の設計および製造に対応したCadenceの設計ソリューションとIPポートフォリオが顧客に提供されることとなる。

GAAとBSPDNは、半導体の低消費電力化と高性能化、そしてSi面積(いわゆるPPA:Power、Performance、Area)の将来的な要件を満たすために必要不可欠とされる技術。今回の協業によって両社が協力して開発を進めるAIドリブンのデジタルおよびアナログ/ミクスドシグナル・リファレンス設計フローには、そうした要件を満たすためのCadenceの複数のソリューションが含まれることとなり、これによりラピダスの顧客は、HBM4や224G SerDes、PCI Express 7.0などを含む、CadenceのインタフェースおよびメモリIPコンポーネントなどを活用し、ラピダスのDesign for Manufacturing and Co-Optimization(DMCO)コンセプトに対応した、2nm GAAとBSPDNの設計および製造ソリューションを活用できるようになるという。