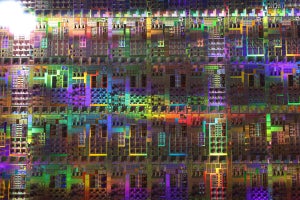

2nmプロセスの半導体の量産を目指すRapidus(ラピダス)は12月10日、同社とIBMの共同研究の成果論文が12月7日~11日にかけて米国サンフランシスコで開催されている半導体の国際学会「国際電子デバイス会議(IEDM 2024)」にて採択されたことを発表した。

発表は現地時間の9日に行われたが、今回の研究では、「SLR(Selective Layer Reductions)」と呼ぶ選択的に層を削減するエッチングプロセスを導入することで、複数のしきい値電圧を制御できるマルチしきい値電圧を備えたナノシートGAA(Gate All Around)のトランジスタを構築できたことが示されたという。

具体的には、高性能コンピューティング向けの超低しきい値電圧と、低電力コンピューティング向けのより高いしきい値電圧を形成することを目的に、SLR1とSLR2と名付けた2つのSLRアプローチを取り入れることで、チャネル間の薄さを維持しつつ、トランジスタとして制御できるようにしたとのことで、IBMでは、このマルチしきい値電圧技術の認定を進め、ラピダスが実際に量産に適用するための移管を目指すとしている。