科学技術振興機構(JST)と岡本工作機械製作所は10月29日、研究成果最適展開支援プログラム(A-STEP) NexTEP-Aタイプの開発課題「シリコン(Si)貫通電極ウェハ全自動研削装置」の開発結果を成功と認定したことを発表した。

同成果は、産業技術総合研究所 先端半導体研究センターの渡辺直也主任研究員の研究成果を基に、JSTが支援し、2016年10月から2024年7月にかけて岡本工作機械製作所において実用化開発が進められたものとなる。

今後の半導体性能向上をけん引する3次元実装技術の課題

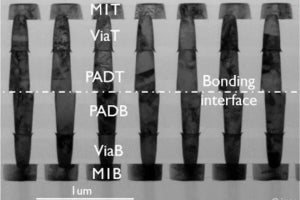

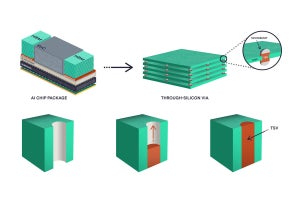

近年、半導体の性能向上をけん引してきたプロセスの微細化が物理的な限界を迎えつつあるが、半導体に対する性能向上ニーズは高まる一方であり、微細化に代わる高性能化技術の実用化が求められている。それを実現する技術の1つとして期待されているのが、半導体チップやダイを立体的に集積させる「3次元実装技術」であり、中でも半導体回路チップを接合用電極の「バンプ」を用いて電気的・機械的に接続しながら垂直方向に積層しようというCuを金属材料部に活用したSi貫通電極(TSV)を用いた手法は積層にかかる面積を抑えられるなどの特徴から期待されている。

このTSVの形成方法は主に、トランジスタ形成と多層配線およびバンプ形成の間に行う「ビアミドルプロセス」と、多層配線およびバンプ形成の後に行う「ビアラストプロセス」の2種類があり、前者は微細なTSVを形成しやすいが、Siウェハを薄化してTSVをウェハ裏面から露出させる際に脆性材料のSiと延性材料のCuを同時研削すると、砥石にCuが目詰まりすることで研削性能の低下を招いてしまうという課題があったという。また、SiウェハにもわずかながらCuが付着、残留するため、回路素子の特性変動など品質低下も懸念されていたとする。

-

ビアミドルプロセスにおける課題(赤点線枠内が、課題の発生する工程)。同プロセスでは、ドライエッチングや洗浄など、高コストで長時間の工程が必要となる。また、TSVの長さにばらつきが生じるため、電極が適切に露出されないことが多く、積層の歩留まりが低下するという課題もあったという (出所:JSTプレスリリースPDF)

これらの課題を防止する安定的な同時研削は困難だとされており、従来手法では、サポートガラス貼り付け後にSiのみを研削し、長時間のSiドライエッチングでTSVをSi内部より出現させ、絶縁膜を成膜した後に化学的機械研磨(CMP)で電極を露出させるという高コストかつ複雑な工程を採用する必要があった。また、TSV形成時のSiウェハ深掘りエッチングの際に、電極ごとの長さにばらつきが生じるため、電極が適切に露出されないことも多く、積層の歩留まりが低下してしまうという課題もあったという。

そのため、ビアミドルプロセスは積層DRAMなどの一部のハイエンドデバイスのみに適用されるプロセスとなっており、今後、3次元実装をさまざまなデバイスに適用していくための低コスト化と歩留まり向上技術の実現が求められていた。こうした背景を踏まえ、今回の取り組みでは、300mmのSiウェハの裏面から研削加工で電極を露出させ、コスト低減および歩留まり向上を実現することを可能とする「Si貫通電極ウェハ全自動研削装置」の開発が進められた。