新エネルギー・産業技術総合開発機構(NEDO)と東北大学、アイシンの3者は10月11日、大容量MRAMを搭載したエッジ領域向け「CMOS/スピントロニクス融合AI半導体」として、アプリケーションプロセッサなど周辺IPまで統合した実証チップを開発したこと、ならびにシステム動作シミュレーションを用いて、従来比で10倍以上となる電力効率と、10分の1以下となる起動時間の改善効果を確認したことを発表した。

同成果は、東北大 電気通信研究所(RIEC)の羽生貴弘所長/教授、同大 国際集積エレクトロニクス研究開発センター(CIES)の遠藤哲郎センター長/教授、同・池田正二教授、同・吉川浩教授、RIECの夏井雅典 准教授らと、アイシンの共同研究チームによるもの。今回の成果は、10月15~18日に幕張メッセで開催されているデジタルイノベーションの総合展「CEATEC 2024」のNEDOブースにて展示される。

エッジ領域での情報処理が求められているが、クラウド領域とは異なり、情報処理に用いることのできる電力量や、サイズなど、利用環境におけるさまざまな制約があるため、それらに適したデバイスの実現が望まれている。

そのような状況を受けてNEDOが実施しているのが、CMOS/スピントロニクス融合技術によるAI処理半導体の設計効率化と実証、およびその応用技術に関する研究開発を目的とした「省エネAI半導体及びシステムに関する技術開発事業」であり、今回の取り組みはその一環として、東北大がCMOS/スピントロニクス融合技術を今後のエッジ向けAI半導体の基盤となる内部メモリとして有効活用すべく、MRAMを用いた自動設計環境の構築とそれに基づく「AIアクセラレータ」の開発を担当。一方のアイシンは、アプリケーションプロセッサほか、周辺IPを統合した実証チップのシステム設計を担当し、この2者の共同研究により、その実証チップの開発が進められた。

現在、小~大規模の多くのAIシステムでは、CPUを内蔵した半導体が活用されているが、そのような半導体の多くが起動用の外付けFLASHメモリ、外付けメモリ(DRAM)および内蔵メモリ(SRAM)を備える構成を標準的なものとしており、演算回路とメモリが離れた配置の「ファーメモリ・コンピューティング構造」となっていると言える。この構成の場合、FLASHメモリに格納されたデータやSRAMやDRAMに一度コピーする必要があり、小規模AIエッジシステムであっても、起動までに相応の時間がかかってしまうという課題がある。

こうした課題に対して、今回の実証チップでは、CPUの起動用とメインメモリ用を兼ねた内蔵メモリと、「重みメモリ」(ニューラルネットワークにおいて入力値の重要性、貢献度を数値化したものを格納するメモリ)に大容量MRAMを採用することで、演算回路とメモリが近くに配置される「ニアメモリ・コンピューティング構造」を実現。その結果、外付けFLASHメモリのバス帯域不足の解消や、CPU上のソフトウェアの起動で必要な多くのプロセスを削減でき、外付けデバイスの初期化時間の削減といった起動時間の短縮が可能になったほか、外付けメモリ容量の削減も実現。システムとしての小型化や低消費電力を可能としたという。

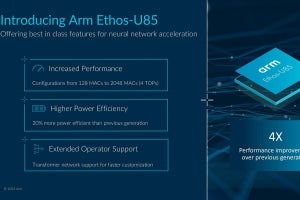

また、今回の実証チップでは、東北大のCIESが開発した低消費電力AIアクセラレータを搭載。TSMCのMRAM混載に対応する16nm FinFETプロセスの「Process Design Kit(PDK)」を用いて開発され、CPUコアにはArm Cortex-A53×2を採用したという。同チップでは、MRAMの採用により、待機電力や動作電力を削減したほか、不揮発化により重みメモリへのロード時間を削減でき、AI処理システム全体の高速起動の実現を可能としたとのことで、RTLでのシステム動作シミュレーションの検証からは、従来比で電力効率10倍以上、および起動時間10分の1以下の改善効果が確認されたという。

なお、今後、研究開発チームではさらに連携を進め、電力効率の詳細評価およびシステム検証を進めるとしているほか、今回の研究成果をいち早く実用化につなげるため、車載機器やサーベイランス機器への応用を計画しているとしている。