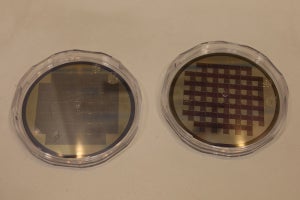

ベルギーimecは、統計的に有意な平均電荷ノイズが1Hzで0.6µeV/√ Hzという、高品質な300mm Siウェハベースのスピン量子ビットの製造プロセスを実証したことを発表した。

同社はノイズ性能の観点から、得られた値について、300mm CMOSプラットフォームで得られた中でもトップクラスの低電荷ノイズ値であるとしており、こうした低ノイズ値により、高い忠実度での量子ビット制御が可能になったとし、300mm Si MOS量子ドットプロセスでこれらの値を繰り返し再現可能に実証することで、Si量子ドットに基づく大規模量子コンピュータの実現に近づけると主張している。

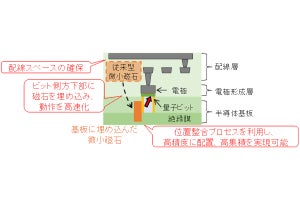

Siベースのスピン量子ビットは、第1に、長い量子コヒーレンス時間 と高忠実度の量子ゲート操作を備えていることが実験室レベルで繰り返し実証されていること、第2に、基礎となるプロセス技術がCMOS製造技術と互換性があり密接に関連しているため、数百万または数十億の量子ビットが同期して動作する大規模量子チップに必要となる量子ドット構造の高度なBEOL相互接続が可能であるという2つの理由から、大規模量子コンピュータ実現に向けた有望な構成要素となっている。

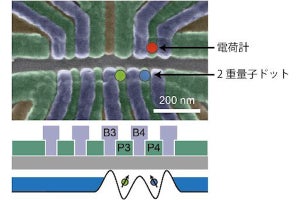

Siベースのスピン量子ビットにはいくつかの種類があり、imecでは、それらすべての種類について研究を進めており、いずれもスピン量子ビットは、電子または正孔の単一のスピンを捕捉するトランジスタ構造に似た金属酸化物半導体(MOS)量子ドット構造によって定義されているという。

長い量子コヒーレンス時間の実現には、ノイズ、特に量子ドットの電荷ノイズを可能な限り低くする必要があるが、このノイズは量子ドットの近くまたは内部に捕捉された残留電荷によって発生するため、それらを除去することがパフォーマンスを向上させる鍵となる。最終的には、量子ドットベースの構造に基づく処理スタックによって決まるが、そこで生じる欠陥を最小限に抑える必要性に変わりはない。これは、プロセスの欠陥を軽減する穏やかなリフトオフプロセスなどのラボベースの技術では実現できるが、サブトラクティブエッチングや露光によるパターニングなどの量産技術では、特に量子ドットの近くのSi/SiO2界面で、デバイスと界面の品質が劣化することがわかっており、その解決が課題となっていた。今回、imecでは、300mmウェハ上でSi/SiO2ベースのMOSゲートスタックを慎重に最適化および設計することで、ウェハ全体で0.6μeV/ √Hz(1Hz時)という低い平均電荷ノイズレベルを達成したと説明している。

同社によると、この値は最先端の製造ベースのSi量子ドット構造と比較した場合、ソースに応じて電荷ノイズレベルが0.5桁から1桁低いことになるとしており、これらの結果は、300mm Si MOSが量子ドットのスピン量子ビットの魅力的な材料プラットフォームであることを裏付けるものだとしている。

また、今回の研究成果について低電荷ノイズデバイスの特性評価に使用された統計分析手法により、その起源に関する基本的な洞察が明らかになったとしており、その原因を踏まえたさらなる最適化に向けた方向性が示されたともしている。

なお今回の技術の詳細は、「Nature Partner Journals」に7月17日付けで掲載されている。