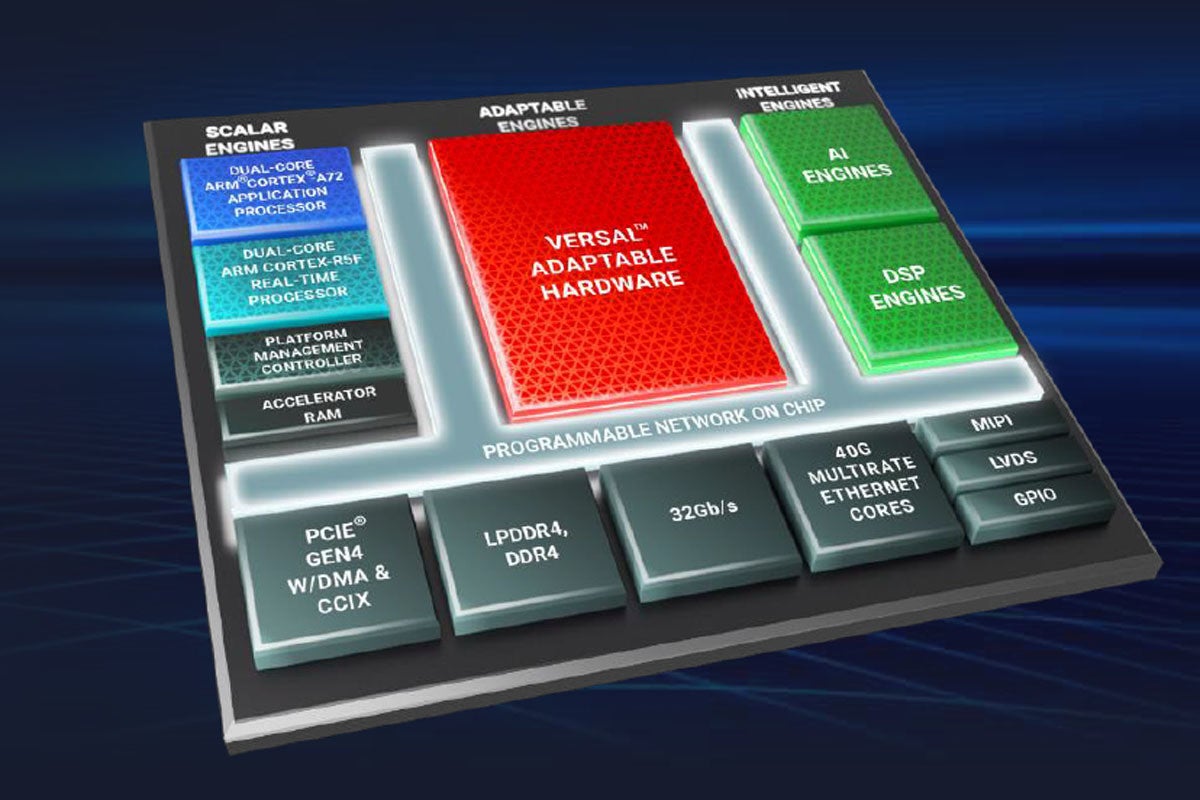

米AMDは米国時間の4月9日、同社のAdaptive SoCである「Versal」シリーズの第2世代製品を発表した。これに関して事前説明会の情報をベースに説明したい。

今回発表されたのは、「Versal AI Edge」と「Versal Prime」のそれぞれ第2世代となる(Photo01)。

まだ事前説明会の時点ではProduct Tableが発表されていないかったので正確なところは不明だが、特徴としては、

- AI Engineの性能/消費電力比を倍増(最大3倍とされるが、根拠は不明)

- 内蔵プロセッサ性能を向上

の2点が挙げられる。

具体的に言えば、

- Processor CoreがDual Cortex-A72+Dual Cortex-R5Fから、Cortex-A78AE×8+Cortex-R52×10に、大幅に強化された。またMali-G78AEも新たに搭載された

- AI Engineが強化された(後述)

- 新たにVideo Encoder/Video Processorが追加された(Video Decoderは以前から搭載されていた)。

- ISPも新たに搭載された

- 主要な機能が、ISO 26262 ASIL-DおよびIEC 61508 SIL-3に対応

といった事が挙げられる(Photo02)。

-

Photo02:これはVersal AI Edge Gen 2であり、「基本的には」ここからAI Engineを抜いたのがVersal AI Prime Gen 2になるはずだが、高速I/Oの類がどの程度強化されているか、などはまだ不明

ことAI Engineについて言えば、昨今のEdge AIのニーズと要求性能の高まりに合わせて性能を向上したという形であるが、それ以外については特に自動車向けや今後は産業機器向けについて、機能安全が必要とされるコア部分に対応できるような強化を行った、というのが正しい認識ではないかと思う。

Cortex-A78AE×8というのはLock Step動作を前提にしたもので、それでも4組のCortex-A78AEが利用できるし、Control ProcessorのCortex-R52×10もLock Step動作のCortex-R52が5組利用できることになる。通常のCortex-A78ではなく、機能安全対応(Lock Step実装済)のCortex-A78AEを選択している事からもこれは明らかだ。これはFunctional Safetyのコア部として利用するのに十分な演算能力であり、初代のVersal AI Primeとかでは外付けのSoCと組み合わせる必要があったのが、このGen 2では外付けSoCが不要ということになる。

そう考えると、Mali-G78AEの搭載にも理解が出来る。車ならメインとなるインスツルメントパネル、産業機器なら状態表示とか制御パネルなどの用途にGPUが利用されるのは一般的であり、それもあってSoCにはGPUが搭載されている。これを代替するためには、当然GPUが必要となる訳だ。

次にAI Engineの話であるが、まず大きな違いとして、

- Compute Tileあたりの演算性能が倍増した

- AI Engineの制御が、Programmable Logic側からAI Engine側に移行した

の2つがある(Photo03)。

-

Photo03:演算性能そのものはともかく、従来の思想はAI EngineはあくまでもAcceleratorであって、これをProgrammable Logic側から呼び出すという格好だったが、この思想を転換。AI EngineはProgrammable Logicと独立して動く格好になった(というか、むしろAI Engineが主?)と考えるのが良いだろう

それともう2つの変更が、MX6/MX9のサポートである(Photo04)。

これは、

- MX9:仮数7bit/指数1bit/符号1bit

- MX6:仮数4bit/指数1bit/符号1bit

であり、実はVitis AI 3.5ではすでにサポートされている(Vitisでサポートされているだけで、既存のハードウェアで動く訳ではないのだが)。世間ではMX4(仮数2bit/指数1bit/符号1bit)というフォーマットもあるが、こちらは未サポートである。で、Photo04にも示されているが、例えばMX6はINT 8のSparceと同等の処理性能ながら、そもそも扱うbit幅が少ない(仮数部で言えばほぼ半分)と言う事もあって、処理に必要な消費電力を減らせるというのがウリになっている。絶対性能そのものも倍増している(これはCompute Tileあたりの演算性能強化で実現している)が、このMX6/MX9を使う事で消費電力を引き下げることにも成功した、という訳だ。

余談だが、このVersal AI Edge Gen 2に搭載されたAI Engine(AIE-ML v2と称されていた)は、XDNA 2と共通という話であった。つまりStrix Pointに搭載されるRyzen AI v2は、このAIE-ML v2の構造を利用したもの、ということである。もっとも構造は同じでもインプリメントには若干の差があるようで、Ryzen AI v2のKernel level programmingは不可能(つまりVITIS AI経由でもできる事に限界がある)という話であった。恐らくRyzen AIはONNX Runtimeを動かすことに注力しており、これに特化したSoftware Stackがインプリメントされており、これの入れ替えは出来ないということではないかと思う。

このVersal AI Edge/Prime Gen2の性能として示されたのは、例えば映像関連(Photo05)では2倍~4倍の性能改善が実現しているとしており、またプロセッサ性能も大幅に向上した(Photo06)としている。

またPhoto02にもあるが、これまでProgrammable Logicで実装されていた処理に関しても、Hard IPの形で実装が増えており、これらを利用する事でより高性能/省電力化が可能になっており、逆にこれらの機能にProgrammable Logicを費やさずに済む分、Programmable Logicのゆとりが増えたともいえる。

現状、とりあえずAI Edgeに関しては少なくとも6製品が予定されている事は明らかにされた(Photo07)。

またスバルが2030年ごろのアイサイト向けに、このVersal AI Edge Gen2を採用する事も発表されている(Photo08)。

すでにドキュメントと一部のツールは対応が終わっており、製品サンプルは2025年前半、評価キットやSOMは2025年中旬、量産は2025年末を予定しているという話である(Photo09)。

ところでこのVersal Prime/AI Edge Gen2だが、製造はなんとTSMCのN6(6nmプロセス)であった。先日発表されたSpartan Ultrascale+がTSMC N7だった事を考えるとちょっと意外ではある。

またVersal Prime/AI Edge Gen2はすべてMonolithic Dieでの提供との事で、Chipletとか3D Stackingなどは一切無いとの事。Versal HBMとかVersal PremiumはMCM構成になっているが、Prime/AI Edge向けはコスト重視と言う事だろうか? ただ今後、このGen 2が他のSKU(HBMとかPremiumとか)にも出て来るか? というとちょっと疑問ではある。というのはProgrammable Logicそのものはほぼ変更が無いようだし、TSMC N7→N6では動作周波数こそ上がる(から、AI EngineやCortex-A78AEの高速動作には有用である)が、トランジスタ密度はそこまで向上しないから、Programmable Logicの高集積にはあまり貢献しない。

元々次世代の製品は5nmをスキップして3nmになるなんて話が流れてきていたが、その根拠はN7→N5だとそれほどトランジスタ密度が上がらないので、N3までスキップしたいというあたりだったはずで、その意味では今回のGen 2製品はProgrammable Logic側への貢献は? というと多少性能/消費電力比が向上はするだろうがその程度でしかないと思われる。ひょっとすると他のGen 2製品は無く、次は2025年以降に3nm製品が出てくる(というか、アナウンスが2025年で出荷は2026年以降?)のではないかと思われる。CPUの世界ではRefresh呼ばわりされる製品が時々あるが、今回はProgrammable Logic以外をかなり強化したので、Refreshという範疇は超えており、それもあってGen 2という言い方にしたのかもしれない。