東京理科大学(理科大)は3月25日、22nm CMOSプロセスで製造した36個のLSIと制御用のFPGA1個を用いて、4096スピンを搭載したスケーラブル全結合型イジングプロセッシングシステムを構築し、スケーラブル化技術の実機検証に成功したことを発表した。

同成果は、同大 工学研究科 電気工学専攻 修士課程2年の惠太一氏、同 修士課程2年の遠藤あかり氏、同大 工学部 電気工学科の河原尊之 教授らによるもの。詳細は2024年1月30日付で国際学術誌「IEEE Access」に掲載された。

LSIで実現するイジングマシンは、量子コンピュータの開発に触発される形で研究が進められている技術分野の1つで、従来のコンピュータよりも組み合わせ最適化問題を高速に解くことができるとされている。しかし、全結合型イジングLSIは、汎用性は高いものの、複雑な配線が必要な全結合であるため、複数個へのチップに分けることが困難と考えられてきたが、河原教授らは2020年、独自の処理アーキテクチャにより、1チップでの全結合型LSIを28nm CMOSプロセス技術を用いて実現したことを報告。その後も、アニーリング方式を用いた1つの全結合システムとして作動する大規模イジングLSIシステムを構成することを目的に、2022年には並列動作させた複数のチップを用いて大規模化を図るスケーラブルな全結合型方式を考案し、FPGAを用いた384スピンの全結合アニーリング処理イジングシステムボードを作成したことを報告していた。

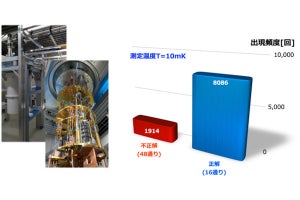

今回の取り組みは、その流れに沿ったもので、22nm CMOSプロセスを用いて製造された36個のLSIと制御用FPGA1個を組み合わせることで、全結合型イジング半導体システムのスケーラブル化技術の実機検証を行おうというもの。開発された4096スピンを持つスケーラブル全結合型イジングプロセッサは従来方式よりも必要チップ数を約半減できる相互作用半減実装方式が採用されたほか、あたかも複数回の動作を一度に行うことができるスピンスレッドを8個搭載することで、1回のデータの出し入れで8回分の計算を可能としており、10MHzで動作し、ボード全体の電力は2.9W、そのうち22nm LSIチップ36個の電力は1.3Wであったという。

例題として、4096頂点の組み合わせ最適化問題の代表的な問題の1つである「頂点被覆問題」を解かせたところ、3.6GHz動作のCPUを持つPCで全結合イジングシステムを模したアニーリングエミュレーションよりも2306倍のエネルギー効率が高い性能であることを確認したほか、。コア部同士での比較では2186倍の電力性能比を達成したことも確認したとする。

なお、研究グループでは今後、今回開発した技術を順調に発展させることができれば、2030年には、2050年頃に量子コンピュータが到達すると予想されている性能と同等の性能である200万個スピンの実現の達成が期待でき、その実演に向けた取り組みを継続して行っていくとしている。

今回の研究成果をまとめた動画(英語版)