英Armは3月13日、自動車向けのプロセッサIPやCSSなどを発表した。これに関して本国よりSuraj Gajendra氏(Photo01)が来日して説明を行われたので、その内容をご紹介したい。

-

Photo01:Suraj Gajendra氏(VP, 自動車 Business)。前職はIntelのVP, AI Products&Strategy, DCAI。その前はArmのVP, Technology and Solutions, 自動車 and IoT Business。さらにその前はIntel。Armには2019年6月~2022年3月まで在籍され、Intelに1年戻ってから2023年5月より現職。丁度新型コロナの時期と被った事もあって、お会いしたのはこれが初めて

元々Armは自動車向けに30年以上IPを提供している(Photo02)というのは、まぁそれを意図してかどうかは兎も角として事実ではあるのだが、現在は自動車向けのマーケットが非常に重要になってきている。

-

Photo02:Lock Stepは2002年のARM 11で最初に提供されたが、ただこれ最初はLock Stepオプションは無かった気がする。最初の車載向け製品というのは、Cortex-A76AEを発表した2018年であるである

2024年第3四半期のRoadshowによれば、自動車のマーケットシェアは2020年の33%から2022年には41%にまで拡大しており、このうちボディ向けECUなどではシェアが低いものの、IVIでは85%以上、ADASやAutonomous Driving(自動運転)では50%以上のシェアを獲得しており、現在ではIVIやADAS/Autonomous Drivingのシェアはさらに上がっていると考えられる、としている。このマーケットに向けてArmはソフトウェアと開発環境、それとハードウェアIPの3つのソリューションを提供している(Photo03)、というのが前置きである。

-

Photo03:このうちソフトウェアに関してはSOAFEEがその代表例である

この2つ目のプロトタイピング環境であるが、要するに仮想環境の提供である(Photo04)。

-

Photo04:“and others”の中にはもちろんSynopsysが入っている。Synopsysは先日Virtual Platformを提供するImperasを買収している。Imperas、直近ではRISC-VのPlatformのアナウンスが目立っているが、元々はArmのVirtual Platformを提供するベンダーだった訳で、この分野では強みになるだろう

SiemensやCadence Design Systems、それと[Corellium(https://www.corellium.com/)]はArmの仮想環境を提供するベンダーであり、さらにEDAツールとの連携も特徴にしている。

AWSやAmpere Computingはその仮想環境を高速に稼働させるためのプラットフォームを提供している。最近だとCorelliumはSOAFEEに対応するCortex-R82の仮想環境の提供を始めており、これと先に述べたソフトウェア環境により、ソフトウェアの開発環境を最大2年短縮できる(Photo05)、というのがArmの主張である。

-

Photo05:ただ、だからといって開発開始を2年遅らせられるというものでもないだろうし、車体の完成の2年前にソフトウェアが開発完了して、その後手直し無しで行けるか? というとそういう話でもないだろう。それでも開発工数が2年分相当減らせる、というのはインパクトのある数字ではある

Armv9ベースで車載分野をローエンドからハイエンドまでカバー

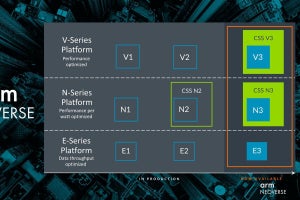

さて、いよいよ本題のプロセッサIPである(Photo06)。今回Armはローエンドからハイエンドまで全体をカバーできるラインナップを用意した。特にハイエンド向けに手厚いのが特徴である。

-

Photo06:このうちSafety-Enabled Cortex-MとAE Mali GPUは今回は特に新製品は無いが、すでに主要なCortex-Mは自動車向けにISO26262 ASIL-B/D対応が完了している

そのハイエンド、今回は「Neoverse V3AE」が発表された(Photo07)。

-

Photo07:NVIDIAのDRIVE ThorがまさにNeoverse V3AEベースで構築されているとの事。ちなみにAVは“Audio Visual”ではなく“Autonomous Vehicle”の略である

何でNeoverse? という話であるが、要するにCortex-X4では性能/消費電力比が悪いのと、スケーラビリティに欠ける(Cortexシリーズ向けのDynamIQは最大14コアまでCPUを接続できるが、これを超える数のCPUコアを接続する事を想定している)ためだそうだ。逆にNeoverse N3ベースでは、性能がやや不足するという。このNeoverse V3AEは要するにLevel 2+以上のAutonomous Drivingの制御向けであって、もちろん実際には他にNPUやGPUなども併用するにしても、CPU性能も必要で、しかもスケーラビリティが必要と言う事になると、一番適切だったのがNeoverse V3だったという事らしい。当然AEということでISO2626 ASIL-Dへの対応が行われているが、逆にNeoverse V3との違いはそれだけという話であった。

このNeoverse V3AEは本当にADAS向けになる訳だが、それより負荷の低いZonalとかVision、IVIとかL2+までの自動運転用途向けには、Cortex-A720AEとCortex-A520AEが用意される(Photo08)。

こちらはCortex-A720/Cortex-A520にISO2626 ASIL-D対応を追加したものである。同様にCortex-R82AEもCortex-R82のISO2626 ASIL-D対応版であるが、Mali-C720AEはまったく新しい製品で、こちらは前方監視カメラとサラウンドカメラの両方に1つで対応できるものということだった(Photo09)。

-

Photo09:Mali-C720AEは内部がComputer VisionとHuman Visionという2つのパイプラインに分割され、最大16個のカメラと8K解像度、4画像出力に対応するもので、かなり強力な構成である

これに加えてArmは、自動車CSS(Compute Subsystems)を提供する事を今回発表した(Photo10)。

これはNeoverse V3AEをベースとしたもので、これにSafety Island(ここはCortex-R82AEが最大16コア実装される)とInterconnect、Security/Debug/IO/Power Management&Clockingから構成される。面白いのは、これはCSSと言いつつも実際にはRTLで提供される(つまり原則としてプロセスには非依存)ことだが、そうは言っても実際には利用するプロセスをある程度想定してやる必要がある。なのだが、例えばサーバー向けのNeoverse CSSの場合、実際に製造するのは翌年とか2年後と比較的短期なのに対し、自動車向けでは4年後とかいう事になるため、プロセスの想定が難しいという話であった。特に自動車向けの場合、TSMCだと通常のプロセスに加えて7nm世代のN7 ADEP(自動車Design Enablement Platform)、N5A、N3AE/N3Aなどの信頼性を高めたプロセスを用意している訳だが、N3AE(Auto Early)は2024年、N3Aは2026年に利用可能となる。本命はこのN3Aになるのだろうが、そうすると2026年まで待たなければならない。ではN5AないしN3AEをターゲットにするか? というとそれも難しいところである。これは他のファウンドリを使った場合も同じで、では通常のプロセスで製造するのか、それとも自動車向けプロセスを使うのか、現在はまだ顧客からのニーズをヒアリングしている最中の様だ。提供そのものは2025年という話なので、現在はまさにインタビューをしている最中なのであろう。

あとこのCSSであるが、内部はCMN-700ベースという話であった。ただ、1つのCMN-700で全体をつなぐ訳ではなく、必要ならCHIを挟んで複数のCMN-700をつないだり、あるいはCHIの先にUCIeをつなぐ事でChiplet構成にしたりと言う事も可能という話であった。逆に言えばCHIとの親和性を考えると、Cortex-AなりCortex-XをベースにするよりNeoverseベースにした方が拡張性を確保できる、という見方もできるだろう(DynamIQでもCHIを使って拡張は可能だが)。

今回発表されたプロセッサIPなどは、すべて同日よりライセンス提供を開始している。CSSに関しては、Neoverse V3AEに関しては先に述べたように2025年から。Cortex-A720AE/A520AEに関しては検討中であり、提供するかどうかを含めて時期などは未定という話であった。