ルネサス エレクトロニクスは2月21日、スピン注入磁化反転型磁気抵抗メモリ(STT-MRAM)のセンスアンプ回路のトリミング手法の工夫および寄生容量低減による高速読み出し技術とテスト工程やセットメーカでの書き込みの高速化技術を開発したことを発表した。併せて、22nmロジック混載MRAMプロセスで製造した10.8MビットMRAMメモリセルアレイを搭載したマイコンを試作し、ランダムアクセス周波数200MHz超ならびに書き換えスループット10.4MB/sを達成したことも発表した。

同成果の詳細は、2月18日~2月22日(米国時間)にて米サンフランシスコにて開催されている「国際固体素子回路会議(ISSCC 2024)」にて2月20日に発表された。

混載プロセスのフラッシュ代替として期待されるSTT-MRAM

エッジ領域でのAI技術活用やIoTの普及などにより、さまざまなエンドポイント領域におけるマイコンの性能も、これまで以上に引き上げることが求められるようになっており、ハイエンドのSoC/MPUが担っていた領域と性能的にオーバーラップするクロスオーバー領域向けマイコン製品を各社が投入するようになっている。

クロスオーバー領域のマイコンの中には、IoT向けなどを中心に、フラッシュメモリを搭載する混載プロセスを採用するものがあるが、フラッシュメモリ混載プロセスは40nmプロセス程度までで、28nmプロセス以下における混載プロセスを考えた場合、MRAMに代替しようという動きが見られている。ルネサスも、MRAM混載マイコンの実用化に向けて研究開発を長年にわたって行ってきており、IEDM 2021にて高速書き込みと低消費電力化技術を、VLSIシンポジウム2022にて高精度ならびに高速読み出し技術を発表してきた。今回の発表は、これらに続くもので、より実用化に向けた高速読み出しと書き換えを実現する技術を開発したものとなる。

-

従来のマイコン領域(ローエンド)とSoC/MPU領域(ハイエンド)の中間に位置するクロスオーバー領域に対するニーズが近年のさまざまな分野における情報処理の高度化に伴い高まってきている (資料提供:ルネサス、以下すべて同様)

センスアンプの2段階トリミングで高速読み取りを実現

MRAMでは、従来のフラッシュメモリと比べて、0と1の状態間の電流差(リードウィンドウ)が小さく高速リードが困難とされてきた。そこで今回は、テスト工程内においてマクロ全体に対し、メモリセル電流の分布測定を実施。参照電流(IREF)が状態間のウィンドウの真ん中となるように読み出し時のビット線電圧を調整する機構を搭載しすることで、まずは全体の粗い調整を実施した後、マクロ内に搭載された各センスアンプのバラつき把握のため、各センスアンプごとのメモリ空間内におけるメモリセル電流分布の実測による、 IREFが状態間のウィンドウの真ん中となるように差動センスアンプの片側にオフセット電流を付加する機構の2段階トリミングを実施することで、リードマージンの拡大を実現したとする。

また、従来回路ではチャネル長変調効果によりセンスアンプのゲインが低下しないようクランプMOSのチャネル長(L)を十分長くする必要があり、併せてそのインピーダンスが高くならないようチャネル幅(W)も大きくする必要があったため寄生容量(ゲート容量)が大きくなってしまい高速動作を妨げる要因となっていたという。そこで今回の取り組みでは、この部分の回路をカスコード接続構成とすることでクランプMOSのチャネル長を長くする必要をなくし、寄生容量の低減を実現。これにおり小さなトランジスタでも構成することを可能としたとする。

-

従来は読み出し時にビット線の電圧が高くなりすぎるとメモリセルの状態が変わってしまう可能性が懸念されていた(リードディスターブ)ため、それを考慮してLとWを大きく取る必要があったが、今回のカイロではカスコード接続構成とすることでチャネル長が短くでき、寄生容量の低減を実現したとする

製造時の高い書き込み電圧を活用して書き込み高速化を実現

一方の書き込み速度の高速化については、IEDM 2021ではマイコンチップの外部電圧(IO用電源)からの降圧により発生した比較的低い書き換え電圧(V1)で全ビットに同時に書き込み電圧を印加して、ほとんどのビットへの書き込みを実施。そこで書き込み漏れが生じた残りのビットだけに高い書き換え電圧(V2)で書き込むことで高速化を果たしていた。ポイントになるのは、V1を高くすると、ビットエラーレートを変えずに、第1段階の書き込みパルス時間を短くできるが、どこまでV1を高くできるかはチップに供給されるIO用電源の下限に寄るところが大きいというところで、今回の取り組みでは、その点を踏まえ、製造の最終工程であるテスト工程や、客先メーカーなどにおける検査・製造ラインでは供給電源が安定している点に着目。そうした状況であればV1を高くできる(V1')ということに着目して、V1'を追加で設定することで、書き込みスループットを従来技術比で1.8倍高速化することを可能としたとする。

セキュリティ確保のためのMTJ-OTP書き込みも可能に

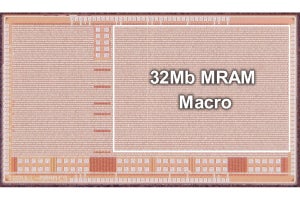

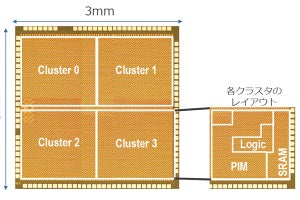

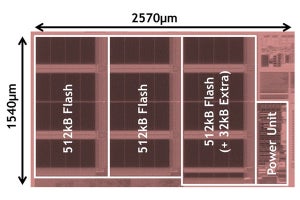

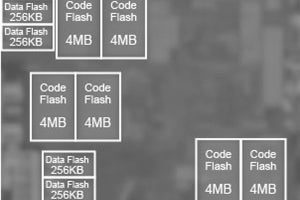

さらに、MRAMのメモリセルは1個のトランジスタと記録素子となる1個の「磁気トンネル接合(MTJ)」とで構成されている点を踏まえ、MTJの絶縁破壊を活用するOTPも開発。実際に、これらの技術を盛り込む形で製造された22nm MRAM混載プロセスによる試作チップでは、4.8Mビット×2および1.2Mビットの合計10.8MビットのSTT-MRAMマクロ領域のほか、0.3MビットのMTJ-OTP領域を別に用意して動作試験などを行ったという。

OTPの書き込みには通常のMRAMへの書き込みよりも高電圧の印加が必要で、供給電圧の安定度が低くなりがちなフィールドでの書き込み難易度が高くなることが懸念されたことから、今回の開発では通常のMRAMの書き込みではメモリアレイの片側に配置したNMOSでソース線を0Vに駆動するのに対して、OTPの書き込みには両側に配置したNMOSを用いることでメモリアレイ内配線の抵抗の影響を抑える手法を採用。これにより一般的な電圧レベルでの書き込みが可能になったという。

実際の試作チップで動作確認を行ったところ、最大接合温度125℃でランダムリードアクセス時間4.2nsを達成したとのことで、これは、MRAM出力データを受けるインタフェース回路のセットアップ時間を考慮しても200MHzを超える周波数でのランダムリード動作を実現することが出来ることが示されたとする。また、書き換えスループット10.4MB/sの達成も確認したという。最大接合温度が、これまで同社が報告したこともある150℃ではなく、125℃での報告としたのは技術的課題があったわけではなく、もともと今回の技術としてはIoTなどの領域向けクロスオーバーマイコンへの適用を想定して開発を進めてきたものであり、当該領域であれば125℃までで対応可能という判断したためだという。技術的には150℃までは対応可能と考えており、車載向けへの適用検討が進めば、改めて評価を行っていくとする。

将来のマイコン製品への適用を検討へ

同社では、今回の技術開発により、試作チップでの実用途を前提としたMRAMマクロエリアの構築や、高速ランダムリード動作、高速書き換えスループットなどが確認できたことで、今後、これまで開発してきた組み込みSTT-MRAM技術を適用したMRAM混載マイコンの製品化検討を前向きに進めていくとしている。ただし実際の製品化のためには、搭載メモリ容量(OTP含む)が、ターゲット市場でどれくらい必要とされることになるのかなどを理解していく必要があるため、すぐに製品が出てくるというわけではない模様だが、技術としてはプロセス問わずに汎用的なものとしており、22nm MRAM混載プロセスの次世代技術となる16nm MRAM混載プロセスでの適用可能だとのことで、製品化の時期については適用プロセスや性能、価格のバランスなどを考慮しながら、ということになりそうである。