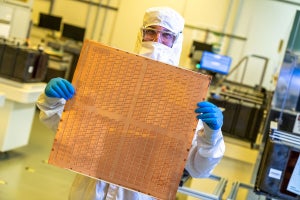

Applied Materials(AMAT)とウシオ電機が12月12日(米国時間)に発表した3D ICパッケージ向けチップレット向け「デジタルリソグラフィ装置(DLT)」。この詳細な内容について、両社の担当者が12月15日(日本時間)に説明を行った。

-

説明を行ったウシオ電機とAMATの担当者。左がウシオ電機のグループ執行役員で事業統括本部Photonics Solutions GBU長であるWilliam F. Mackenzie氏、右がAMATグループバイスプレジデント兼セミコンダクタ プロダクトグループ ジェネラルマネージャーのSundar Ramamurthy氏

より高性能な2.5D/3Dパッケージングを実現するための課題

現在、半導体の高性能化はムーアの法則をけん引してきたプロセスの微細化が困難になってきたことを踏まえ、2.5D/3Dパッケージング技術、近年では中工程と呼ばれる分野に期待が集まるようになってきた。

2.5D/3Dパッケージングは、複数のしかもさまざまな種類の半導体チップ/ダイを1パッケージ上に集約しようという技術である。より多くの半導体チップ/ダイを1パッケージ内に収めようとすると、パッケージサイズが大型化し、パッケージ全体を複数回露光してパターンをつなぎ合わせるスティッチングを行う必要が出てくるほか、1パッケージ内に多くの半導体チップ/ダイがヘテロジニアスに集約されることになるため、そのハンドリングそのものを高精度に行う必要もでてくる。両社は今後、そうしたさらなる高集積化にされたサブストレート(基板)を実現するためには、基板上の配線幅を狭くする必要が出てくるほか、従来の樹脂のみならずガラスのような新素材への対応なども必要となってくることを踏まえ、協力して新たな技術開発に取り組むことで合意し、開発を進めてきたという。

AMATとウシオ電機がそれぞれの強みで役割を分担

DLTの開発に当たっては、電子ビーム(EB)描画技術などのノウハウを有するAMATが研究開発を担当し、ウシオ電機が量産製造、販売を担当するという役割分担がなされているという。ただし、ウシオ電機のグループ執行役員で事業統括本部Photonics Solutions GBU長であるWilliam F. Mackenzie氏は、「どこからが製造・販売で、どこからが研究開発か、ということをきっちりと線引きをしているわけではない。そこをオーバーラップしつつ、柔軟に協力して進めて行こうというのが我々のパートナーシップという意味合いだ」と説明し、ウシオ電機としての技術ノウハウなども活用されていることを説明する。ただ、販売についてはウシオ電機のみで、AMATから提供されることはないという。

DLTの仕組みは、レーザー光源から照射された紫外光をMEMS技術を活用して無数のデジタルマイクロミラーをチップ上に形成した「Digital Micromirror Device(DMD)」に照射し、所望のパターンデータをマスクレスで基板に描画しようというもの。DMDを活用するという点でデジタルリソグラフィだという。「マスクレスであることもあり、コスト負担はそれほど大きくない」とするほか、「基板は必ずしもフラットな状態というわけではなく反っていたりするが、さまざまな基板上のポイントからのデータを把握することで、レーザービームを基板の反りを考慮した形で処理することができるため、多少の反りが生じていても問題なくパターンを形成することが可能。これにより確実にパッドやビアを形成でき、高密度化も可能になる」とし、DLTという技術がこれから重要なものになっていくであろうとの見解を示した。

アドバンストパッケージ向けリソ市場は5年間で3倍に拡大

AMATとウシオ電機の試算によると、アドバンストパッケージ向けリソグラフィ市場規模(SAM)は2025年で2億5000万ドル、これが2030年には3倍強の8億ドルまで成長することが見込まれるという。ちなみに、すでに2社の顧客のもとで評価が行われており、ガラス基板でも樹脂基板でも良好な性能を発揮できることを示しているという。

なお、AMATとウシオ電機では、この市場成長性をけん引するのはHPCやAIでの高性能半導体と見ており、そうした加速する高性能半導体向けパッケージング市場に対応できるよう協力して、両社の技術のいいところを持ち寄っていくことで、顧客のバリューをさらに加速させていきたいとしている。