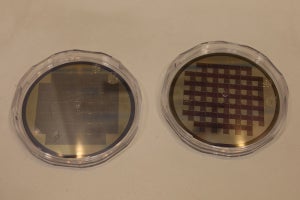

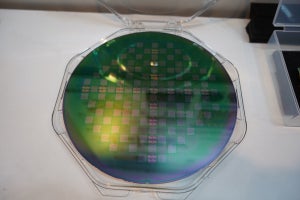

東京ビッグサイトにて12月13日~15日にかけて開催されているエレクトロニクス製造サプライチェーンの国際展示会「SEMICON Japan 2023」の「第4回 量子コンピューティングパビリオン」にて、富士通が64量子ビット超伝導量子コンピュータ向けチップの実物を展示している。 同チップは理研RQC-富士通連携センターに2023年10月に設置された超伝導量子コンピュータに搭載されているものと同じもの。3次元コンタクト構造を採用することで、1チップでは64量子ビットながらタイル状に複数チップを配置することで量子ビットの数を増やすことができるという特徴を有している。

なお、富士通では2023年10月からの64量子ビット量子コンピュータによる量子アプリケーションの実機検証を踏まえ、2025年には256量子ビットを実現しつつ、エラー訂正技術を実装した超伝導量子コンピュータの公開を目指すとするほか、2026年以降には1000量子ビット超の超伝導量子コンピュータの公開を目指すとするロードマップを公開しており、平行して最適なエラー訂正技術の探索なども行っていくことで、将来の社会課題の解決につなげていきたいとしている。