電気通信大学(電通大)は11月10日、従来よりも10倍以上の高密度かつ、細線直径の標準偏差が10%以下の高均一な「インジウムヒ素(InAs)量子ナノワイヤ」をシリコン(Si)基板上に作製する技術を開発したことを発表した。

同成果は、電通大 基盤理工学専攻の山口浩一教授、同・中川竜輔大学院生らの研究チームによるもの。詳細は、米国物理学協会が刊行する応用物理学を扱う学術誌「Journal of Applied Physics」に掲載された。

半導体量子ナノワイヤ(量子細線)とは、半導体を細線構造化したもので、細線の直径が電子の波長以下(数nm~数十nm)程度の柱状に成長させた2次元的な量子閉じ込め構造を特徴とする。量子ナノワイヤは、次世代の縦型トランジスタやメモリのほか、量子ナノセンサや量子細線レーザ、量子構造太陽電池などの光電子デバイスへの応用が見込まれている。中でも、InAsなどのIII-V族半導体はその特異な光電子物性から、デバイスの高機能化に貢献することが期待されている。

そうした高機能な次世代デバイスに応用するには、量子ナノワイヤのサイズ制御や高密度化などの基盤技術の開発が重要だ。しかし、これまでの大半のナノワイヤ成長技術においては、直径が100nm~数百nmと比較的太いものが多く、電子の量子閉じ込め効果が十分ではなかったという。量子サイズ効果を発現させるには、InAsナノワイヤの直径を40nm以下にする必要があり、さらにこの微小な量子ナノワイヤ構造を高密度かつ高均一に作製する結晶成長技術が望まれていた。

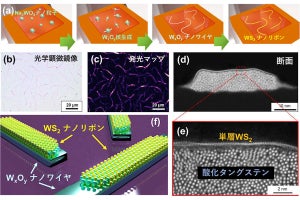

そこで研究チームは今回、高密度で高均一な量子ナノワイヤ構造の作製に向け、「分子線エピタキシー(MBE)法」を用いて、Si基板表面の酸化膜にガリウム(Ga)ナノ液滴を堆積し、基板加熱による反応過程によってnmサイズの穴(ピンホール)を形成する手法を用いたという。なおMBE法とは、超高真空の容器内で、加熱した基板上に高純度の成長原料を分子ビーム状にして照射させ、単結晶薄膜を成長させる手法のことだ。

この手法では、Ga液滴の供給量や反応温度、Si酸化膜表面の清浄化が重要なポイントとなるとのこと。中でも酸化膜表面の清浄化に関しては、電子線の照射による表面への炭素などの吸着がピンホールの形成を阻害してしまうことが確認されたとする。このことから、表面構造の観察に用いる電子線照射や、表面パターン形成のための電子線照射などのプロセスは避ける必要があることが解明された。

このようにしてSi酸化膜に高品質なピンホールを作製した上で、ピンホール底のSi基板結晶からInAs単結晶核を形成し、高さ方向の成長が促進された六方晶(ウルツ鉱構造)のInAsナノワイヤが高密度かつ高均一に形成された。

結晶成長実験では、面内密度が1~2×1010cm-2のInAsナノワイヤが再現性高く得られ、従来のナノワイヤの10倍~100倍もの高い密度で形成できたとする。また、ナノワイヤ構造以外の堆積物や多結晶粒の形成も抑制できることから、直径30nm以下の細いナノワイヤ構造を制御性高く作製することが可能になり、これによって量子サイズ効果を発現する量子ナノワイヤを標準偏差8.8%と高均一に作製することに成功したとしている。

-

(左)直径の異なるInAsナノワイヤの発光スペクトル。(右)InAsナノワイヤ直径と発光ピークエネルギーの関係(WZ:ウルツ鉱構造、ZB:閃亜鉛鉱構造)。量子サイズ効果によってバルク結晶よりも発光エネルギーは高エネルギー化し、量子ナノワイヤの直径を変化させることにより発光エネルギーを制御することができる(出所:電通大プレスリリースPDF)

研究チームは今回の研究により、高密度で高均一な半導体量子ナノワイヤをSi基板上に作製することに成功し、Si基板に集積する次世代の縦型トランジスタやメモリのほか、「量子ドット」構造を内蔵した量子細線レーザや量子構造太陽電池、量子ナノセンサなどの量子デバイスの高機能化や超集積化が可能になることが期待されるとする。

そして研究チームは今後、異種半導体結晶のヘテロ接合を導入したコア・シェル構造の量子ナノワイヤや量子ドットナノワイヤの作製を行い、量子デバイス応用について検討する予定としている。